# McGraw-Hill HANDBOOKS

Featuring:

High Density

Interconnect

COOMBS'

# PRINTED CIRCUITS HANDBOK FIFTH EDITION

# PRINTED CIRCUITS HANDBOOK

Clyde F. Coombs, Jr. Editor-in-Chief

**Fifth Edition**

McGRAW-HILL

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto

### Cataloging-in-Publication Data is on file with the Library of Congress

### McGraw-Hill

A Division of The McGraw-Hill Companies

Copyright © 2001, 1996 by The McGraw-Hill Companies, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

7 8 9 10 DOC/DOC 0 5 4 3 2 1 0

ISBN 0-07-135016-0

The sponsoring editor for this book was Steven Chapman, the production supervisor was Pamela Pelton. It was set in Times Roman by North Market Street Graphics.

Printed and bound by R.R. Donnelley & Sons Company.

McGraw-Hill books are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. For more information, please write to the Director of Special Sales, McGraw-Hill, Inc., 11 West 19th Street, New York, NY 10011. Or contact your local bookstore.

Information contained in this work has been obtained by The McGraw-Hill Companies, Inc. ("McGraw-Hill") from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein, and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

This book is printed on recycled, acid-free paper containing 10% post-customer waste.

## **CONTENTS**

List of Contributors xxxvii

**Part 1 Introduction to Printed Circuits**

Chapter 1. Electronic Packaging and High-Density Interconnectivity

xxxix

Preface

| 1.1 Introduction / 1.3                                                                             |     |

|----------------------------------------------------------------------------------------------------|-----|

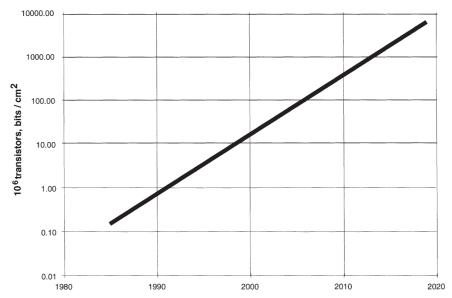

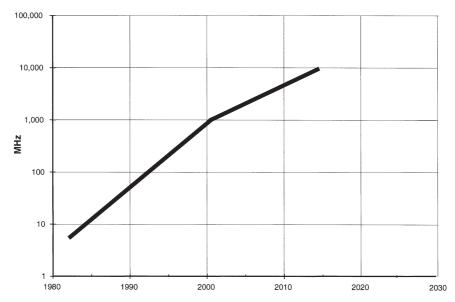

| 1.2 Measuring the Interconnectivity Revolution (HDI) / 1.3                                         |     |

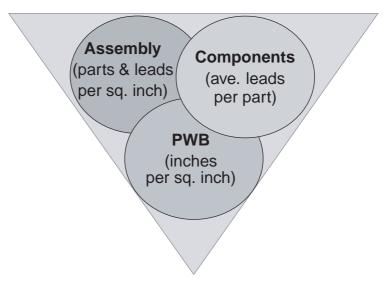

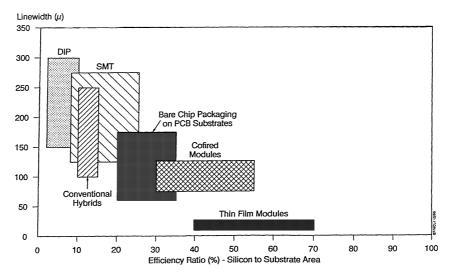

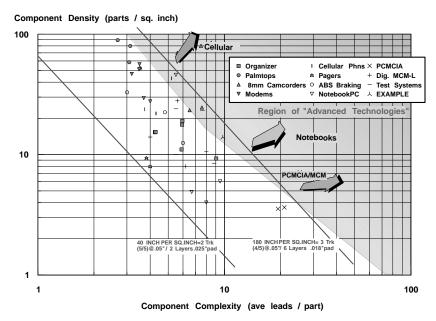

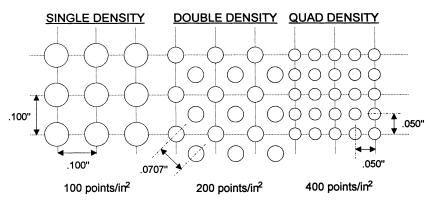

| 1.2.1 Interconnect Density Elements / 1.4                                                          |     |

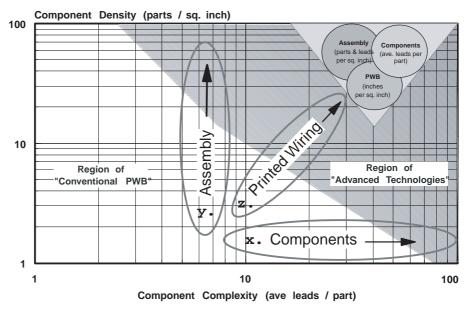

| 1.2.2 Interconnect Technology Map / 1.4                                                            |     |

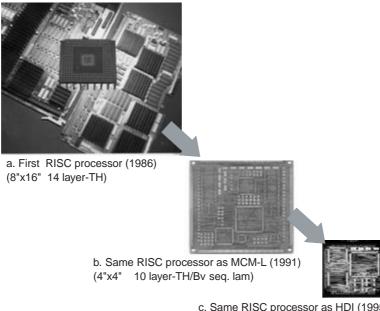

| 1.2.3 An Example of the Interconnect Revolution / 1.5                                              |     |

| 1.2.4 Region of Advanced Technologies / 1.6                                                        |     |

| 1.3 Hierarchy of Interconnections / 1.6                                                            |     |

| 1.4 Factors Affecting Selection of Interconnections / 1.7                                          |     |

| 1.4.1 Speed of Operation / 1.7                                                                     |     |

| 1.4.2 Power Consumption / 1.8                                                                      |     |

| 1.4.3 Thermal Management / 1.8                                                                     |     |

| 1.4.4 Electronic Interference / 1.8                                                                |     |

| 1.4.5 System Operating Environment / 1.9                                                           |     |

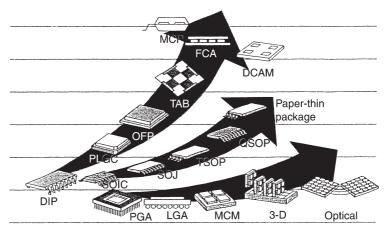

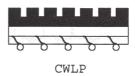

| 1.5 ICs and Packages / 1.10                                                                        |     |

| 1.5.1 IC Packages / 1.10                                                                           |     |

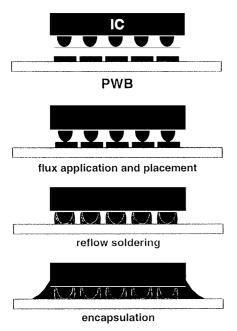

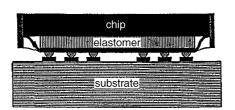

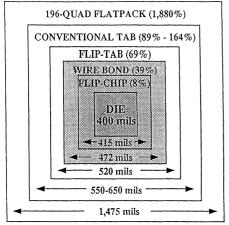

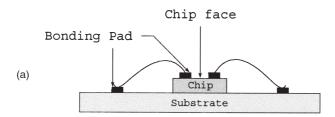

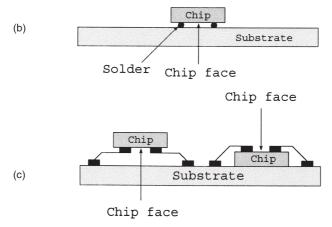

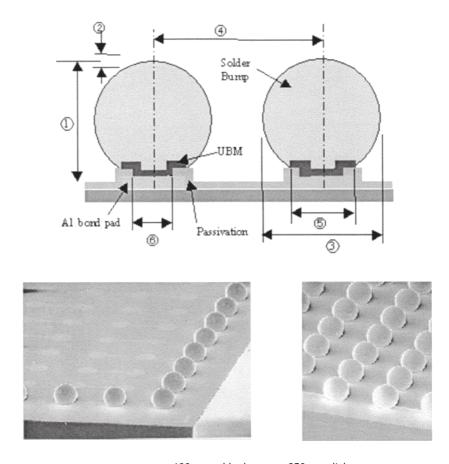

| 1.5.2 Direct Chip Attach / 1.12                                                                    |     |

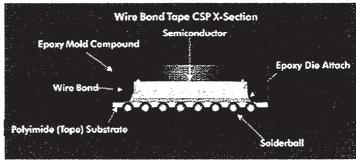

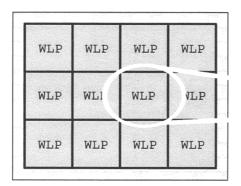

| 1.5.3 Chip-Scale Packages (CSPs) / 1.13                                                            |     |

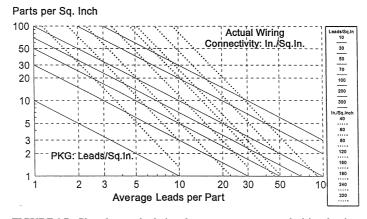

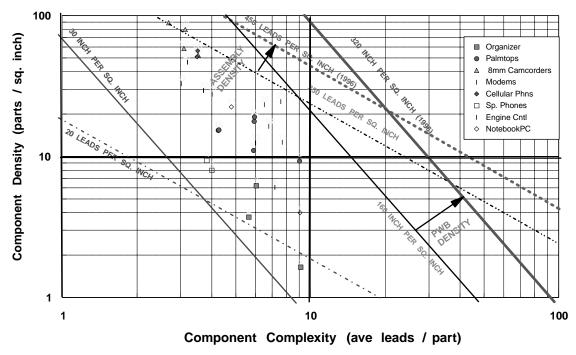

| 1.6 Density Evaluations / 1.14                                                                     |     |

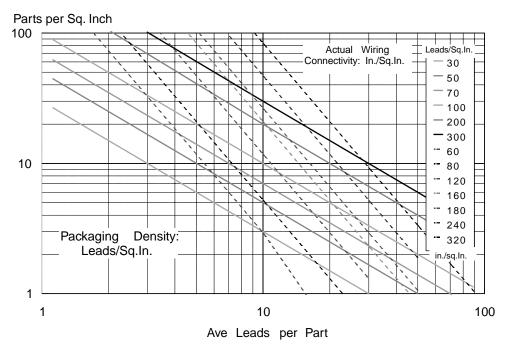

| 1.6.1 Component Density Analysis / 1.14                                                            |     |

| 1.6.2 PWB Density Metrics / 1.14                                                                   |     |

| 1.6.3 Special Metrics for Direct Chip Attach (DCA) / 1.15                                          |     |

| 1.7 Methods to Increase PWB Density / 1.16                                                         |     |

| 1.7.1 Effect of Pads on Wiring Density / 1.17                                                      |     |

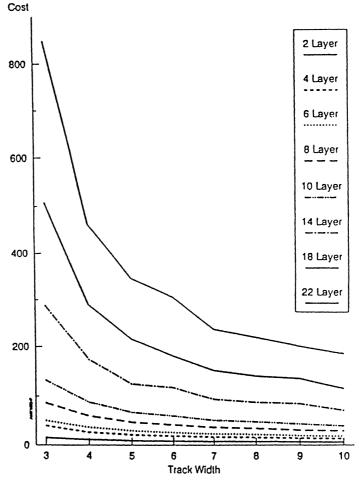

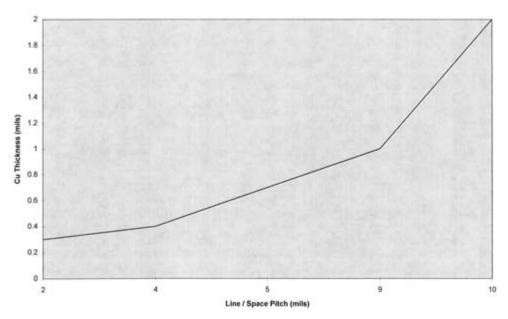

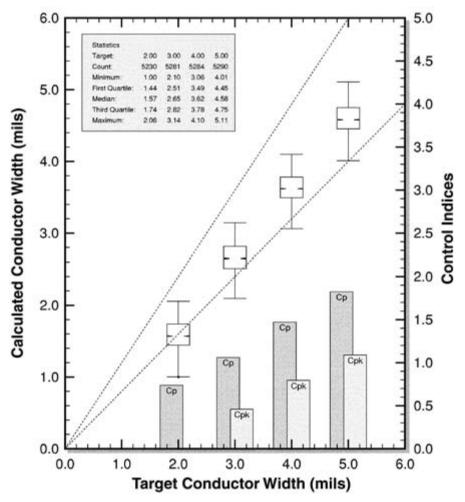

| 1.7.2 Reduction of Conductor Width / 1.18                                                          |     |

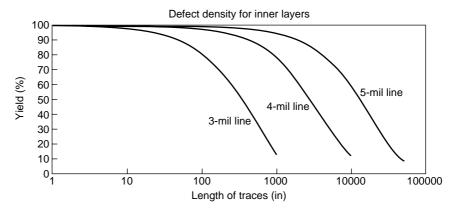

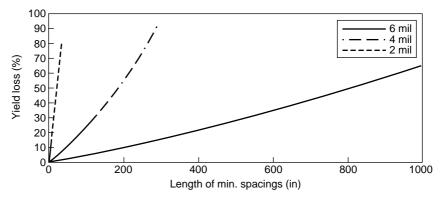

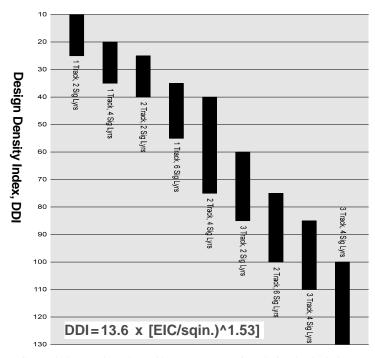

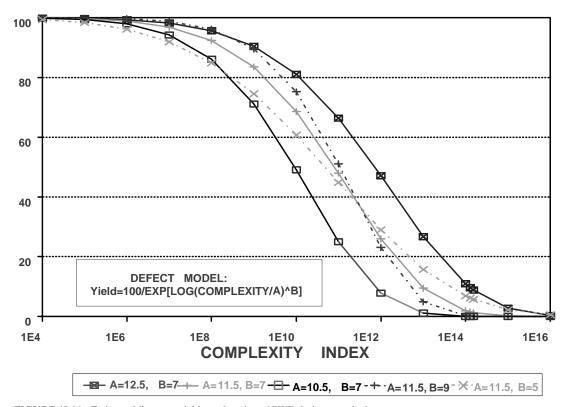

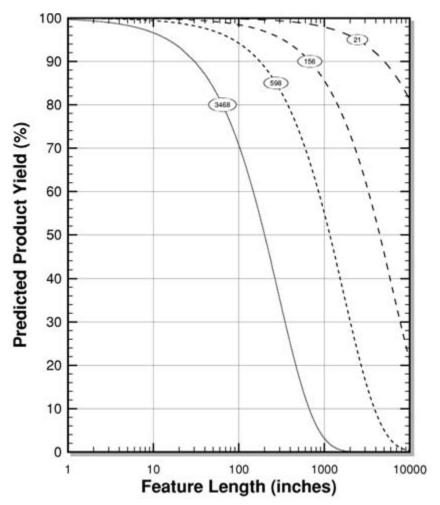

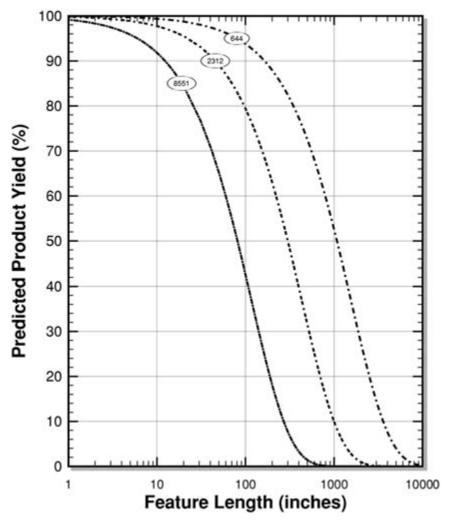

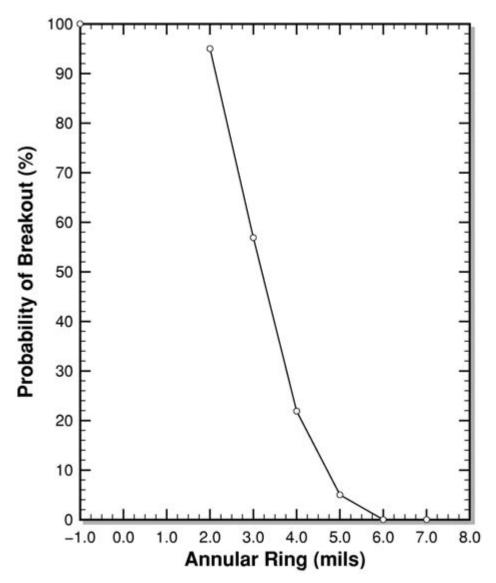

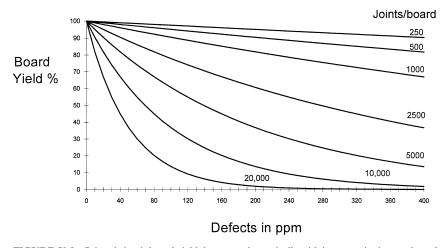

| 1.7.2 Reduction of Conductor Width / 1.70  1.7.3 Effect of Conductor Widths on Board Yields / 1.19 |     |

| 1.7.4 Increase in Number of Conductor Layers / 1.21                                                |     |

| References / 1.21                                                                                  |     |

| References / 1.21                                                                                  |     |

| Chanter 2 Comison dustor Dockoring Tooknology                                                      | 2.1 |

| Chapter 2. Semiconductor Packaging Technology                                                      | 2.1 |

|                                                                                                    |     |

| 2.1 Introduction / 2.1                                                                             |     |

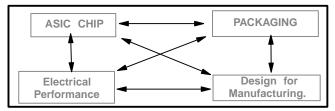

| 2.1.1 Packaging and Printed Circuit Technology Relationships / 2.3                                 |     |

| 2.1.2 Electronic Packaging Issues and Concerns / 2.4                                               |     |

| 2.1.3 Requirements for Electronic Systems / 2.5                                                    |     |

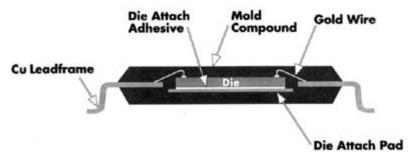

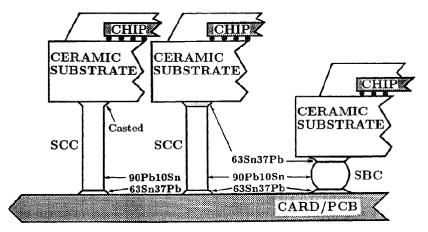

| 2.2 Single-Chip Packaging / 2.5                                                                    |     |

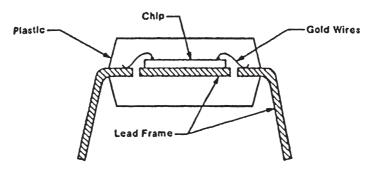

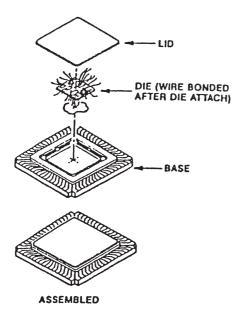

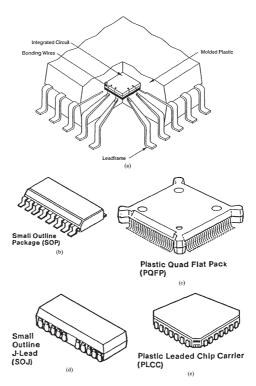

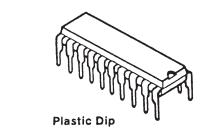

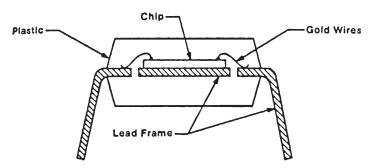

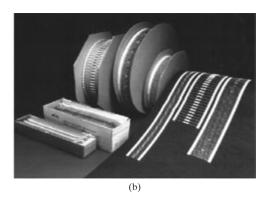

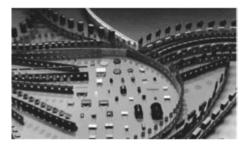

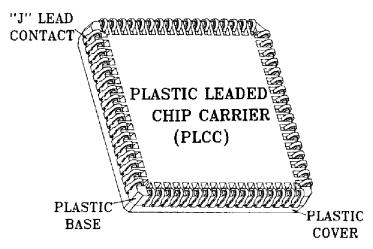

| 2.2.1 Dual Inline Packages (DIPs) / 2.6                                                            |     |

| 2.2.2 Leadless Ceramic Chip Carriers / 2.6                                                         |     |

| 2.2.3 Plastic Quad Flat Package (PQFP) / 2.7                                                       |     |

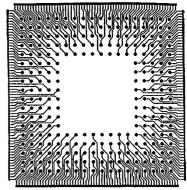

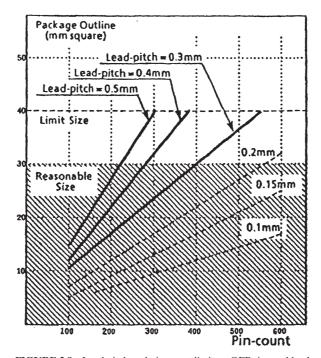

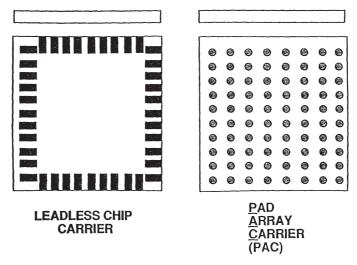

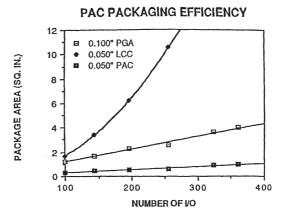

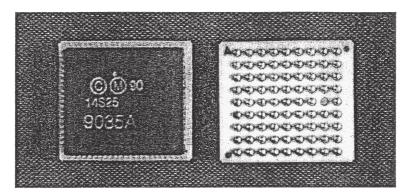

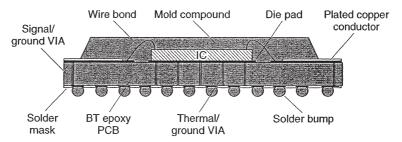

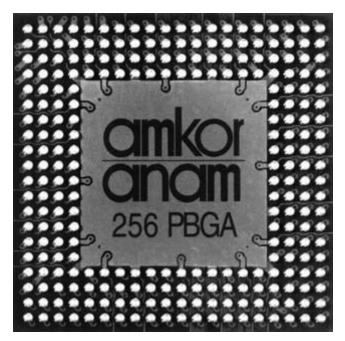

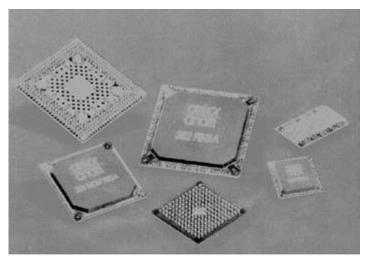

| 2.2.4 Pin Grid Array (PGA) and Pad Array Carrier (PAC) / 2.8                                       |     |

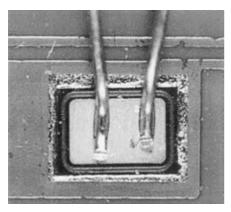

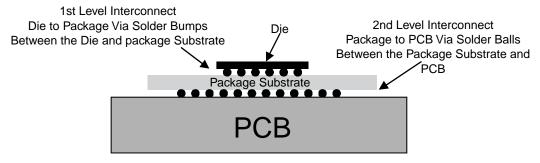

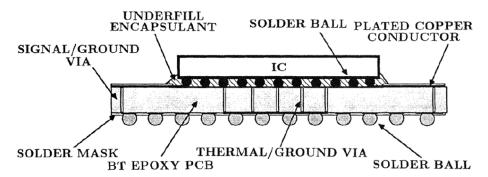

| 2.2.5 Direct Chip Attach (DCA) / 2.12                                                              |     |

|                                                                                                    |     |

|                                                                                                    |     |

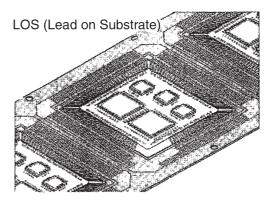

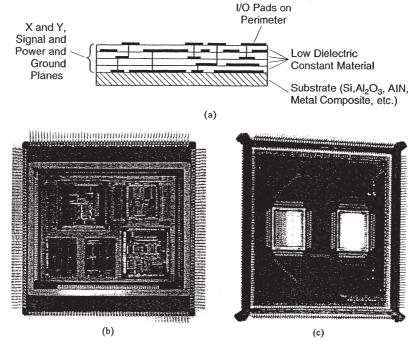

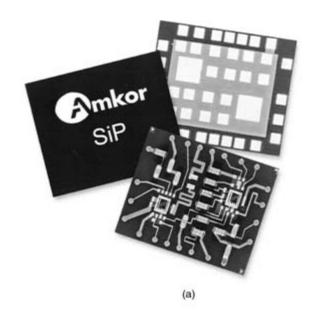

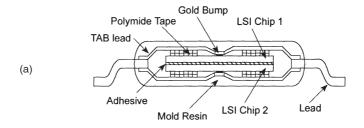

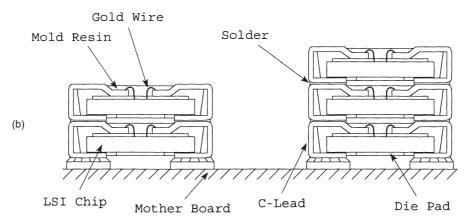

| 2.3 Multichip Packages / 2.15 2.3.1 Multichip vs. Single-Chip Packages / 2.15 2.3.2 MCPs Using Printed Circuit Technology / 2.16 2.3.3 MCP s Using Organic Substrates / 2.16 2.3.4 MCP and PGA / 2.17 2.3.5 Multichip Stacked-Die Packages / 2.17 2.3.6 MCP and Known Good Die / 2.17 2.3.7 System-in-a-Package / 2.18 2.4 Optical Interconnects / 2.18 2.4.1 Components and Packages / 2.20 2.4.2 Advantages of Optical Interconnects / 2.21 2.5 High-Density/High-Performance Packaging Summary / 2.21 2.6 Roadmap Information / 2.21 References / 2.21                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 3. Advanced Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.1 |

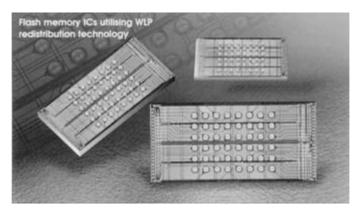

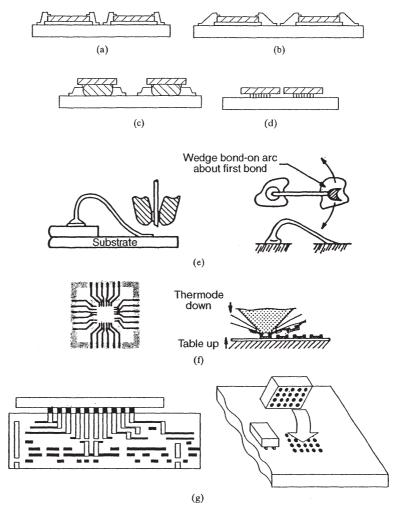

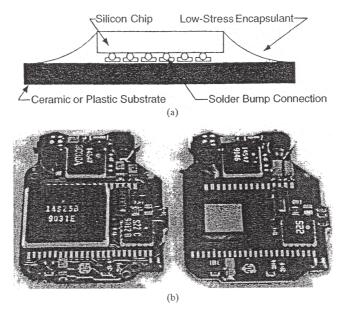

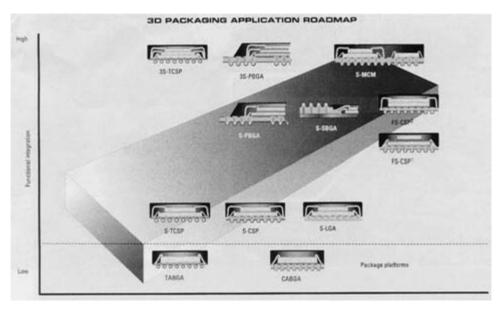

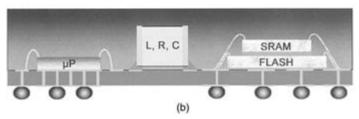

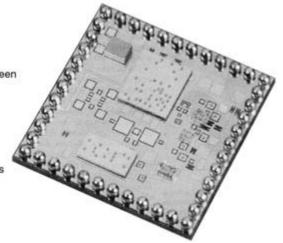

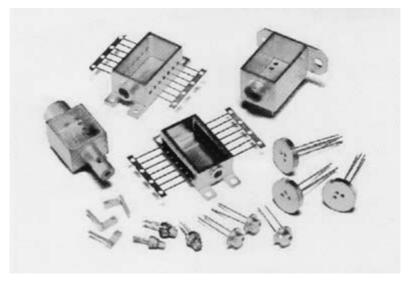

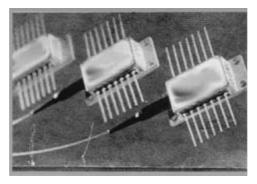

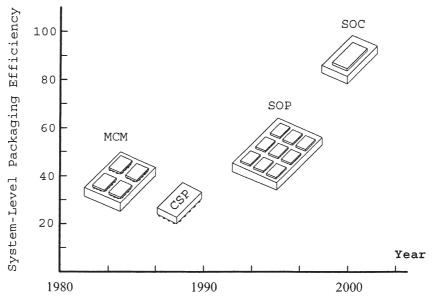

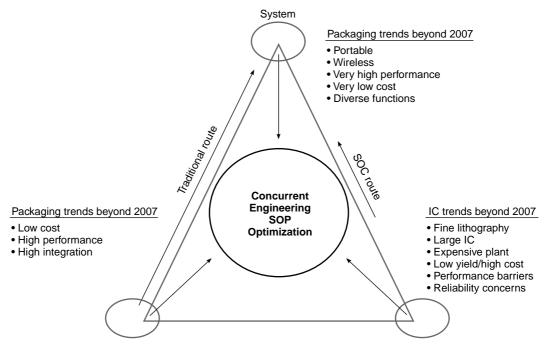

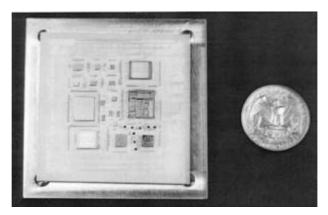

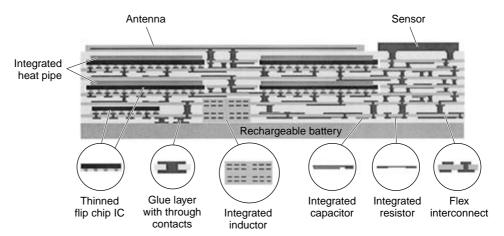

| 3.1. Introduction / 3.1 3.1.1 Package Drivers / 3.1 3.1.2 Packaging as a Basic Design Element / 3.2 3.2 System-on-a-Chip (SOC) vs. System-on-a-Package (SOP) / 3.3 3.2.1 SOC / 3.3 3.2.2 SOP / 3.4 3.3 Multichip Modules / 3.5 3.3.1 MCM-D / 3.7 3.3.2 MCM-C / 3.9 3.3.3 MCM-L / 3.11 3.3.4 MCM-D/C / 3.13 3.5 MCM-D/L / 3.13 3.4 Multichip Packaging / 3.14 3.4.1 Few-Chip Packaging (FCP) / 3.14 3.4.2 Partitioned Silicon (Tiling) / 3.15 3.4.3 Chip-Scale Packaging (CSP) / 3.16 3.4.4 Wafer-Scale Integration (WSI) / 3.17 3.4.5 Three-Dimensional (3-D) Packaging / 3.17 3.5 Enabling Technologies / 3.19 3.5.1 Known Good Die (KGD) / 3.19 3.5.2 Chip Thinning / 3.19 3.5.3 Chip Attach / 3.20 3.5.4 Chip-on-Board (COB) / 3.21 3.5.5 Passive Devices / 3.23 3.6 Drivers for Advanced Packaging / 3.25 3.6.1 Materials / 3.26 3.6.2 Lead-Free / 3.26 3.6.3 Micro-Electro-Mechanical and Micro-Opto-Electro-Mechanical Systems / 3.26 3.6.4 Tachaplage Devices pand Trando / 3.27 |     |

| 3.6.4 Technology Developments and Trends / 3.27 References / 3.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| Chapter 4. Types of Printed Wiring Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.1 |

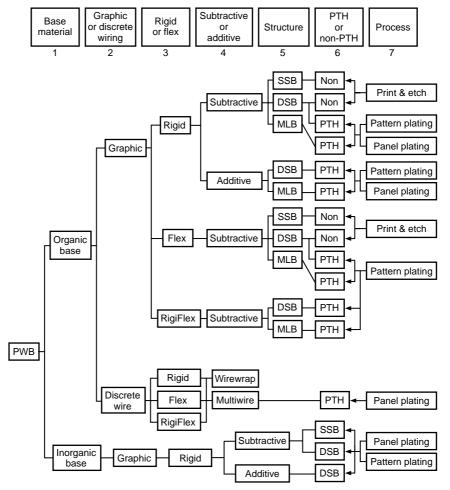

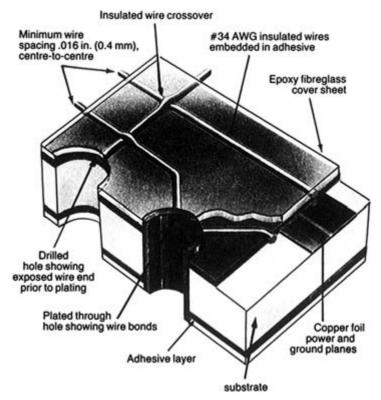

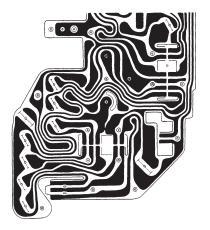

| <ul> <li>4.1 Introduction / 4.1</li> <li>4.2 Classification of Printed Wiring Boards / 4.1</li> <li>4.2.1 Basic PWB Classifications / 4.1</li> <li>4.3 Organic and Nonorganic Substrates / 4.3</li> <li>4.3.1 Organic Substrates / 4.3</li> <li>4.3.2 Nonorganic Substrates / 4.3</li> <li>4.4 Graphical and Discrete-Wire Boards / 4.3</li> <li>4.4.1 Graphical Interconnection Board / 4.3</li> <li>4.4.2 Discrete-Wire Boards / 4.4</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

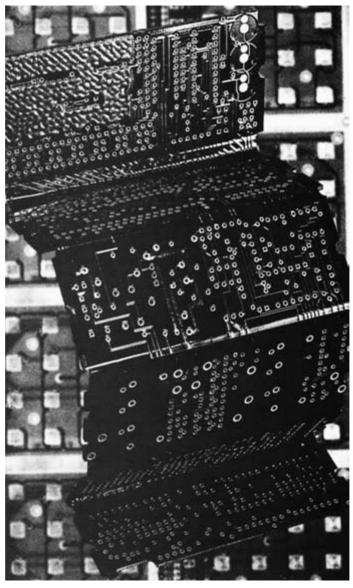

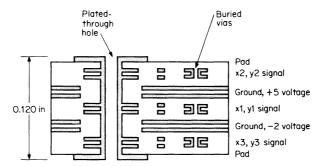

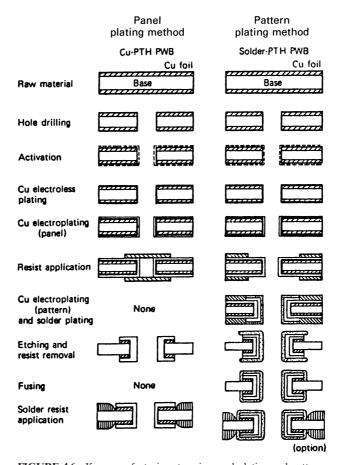

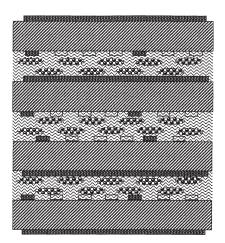

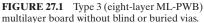

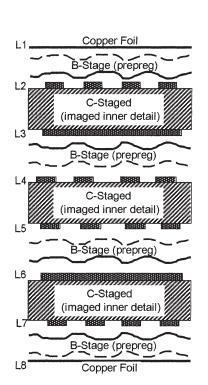

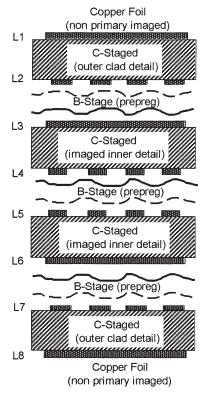

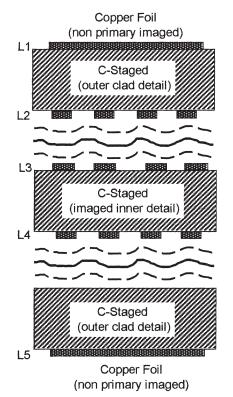

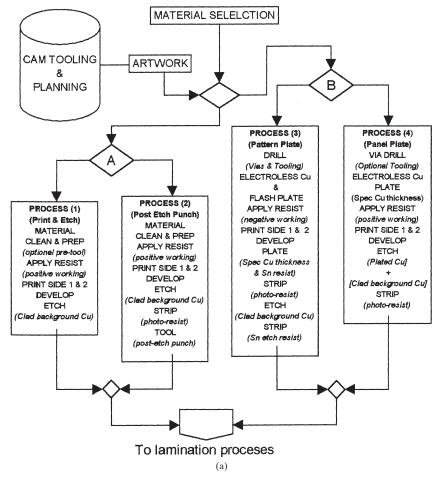

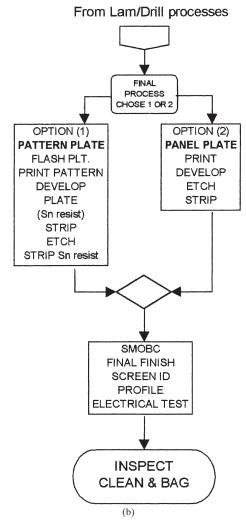

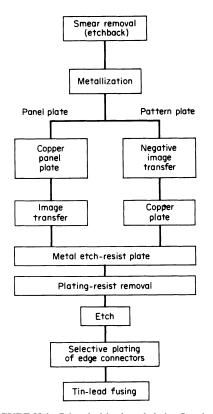

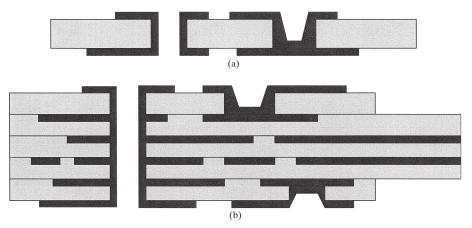

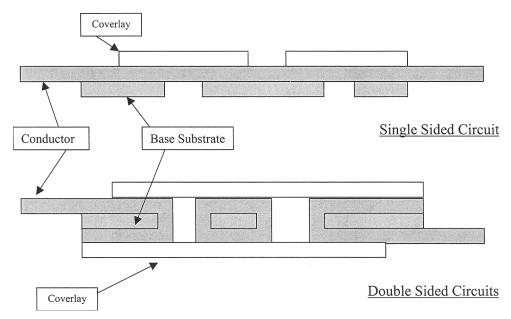

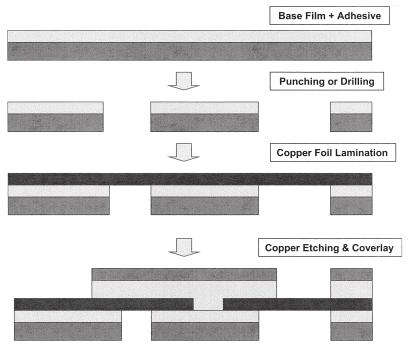

| <ul> <li>4.5 Rigid and Flexible Boards / 4.5</li> <li>4.6 Graphically Produced Boards / 4.6</li> <li>4.6.1 Single-Sided Boards (SSSs) / 4.6</li> <li>4.6.2 Double-Sided Boards / 4.7</li> <li>4.6.3 Multilayer Boards (MLBs) / 4.8</li> <li>4.7 Molded Interconnection Devices / 4.10</li> <li>4.8 Plater-Through-Hold (PTH) Technologies / 4.10</li> <li>4.8.1 Subtractive and Additive Processes / 4.10</li> <li>4.8.2 Pattern Plating / 4.11</li> <li>4.8.3 Panel Plating / 4.13</li> <li>4.8.4 Additive Plating / 4.13</li> <li>4.9 Summary / 4.13</li> <li>References / 4.14</li> </ul>                                                                                                                                       |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Part 2 Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| Chapter 5. Introduction to Base Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.3 |

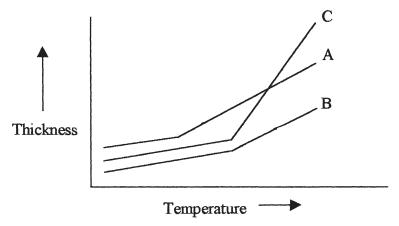

| <ul> <li>5.1 Introduction / 5.3</li> <li>5.2 Grades and Specifications / 5.3</li> <li>5.2.1 NEMA and IPC Grades / 5.3</li> <li>5.2.2 Glass Transition Temperature / 5.4</li> <li>5.3 NEMA Industrial Laminating Thermosetting Products / 5.7</li> <li>5.4 IPC-4101 Specification for Base Materials for Rigid and Multilayer Printed Boards / 5.9</li> <li>5.5 FR-4 Issues / 5.9</li> <li>5.5.1 The Many Faces of FR-4 / 5.9</li> <li>5.5.2 The Longevity of FR-4 / 5.9</li> <li>5.6 Laminate Identification Scheme / 5.10</li> <li>5.7 Prepreg Identification Scheme / 5.13</li> <li>References / 5.14</li> </ul>                                                                                                                 |     |

| Chapter 6. Base Material Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1 |

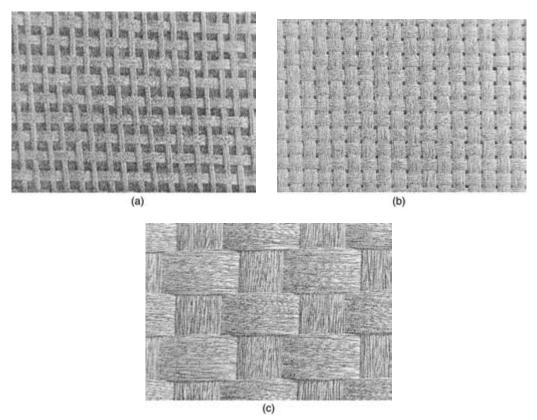

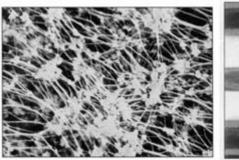

| 6.1 Introduction / 6.1 6.2 Epoxy Resin Systems / 6.1 6.2.1 Definition of Epoxy / 6.1 6.2.2 Difunctional Epoxies / 6.2 6.2.3 Tetrafunctional and Multifunctional Epoxies / 6.3 6.3 Other Resin Systems / 6.3 6.3.1 Epoxy Blends / 6.4 6.3.2 Bismaleimide Triazine (BT)/Epoxy / 6.4 6.3.3 Cyanate Ester / 6.4 6.3.4 Polyimide / 6.4 6.3.5 Polyester / 6.5 6.3.6 Polytetrafluoroethylene (PTFE, Teflon®) / 6.5 6.3.7 Allylated Polyphenylene Ether (APPE) / 6.5 6.4 Additives / 6.5 6.4.1 Curing Agents and Accelerators / 6.5 6.4.2 Flame Retardants / 6.5 6.4.3 Ultraviolet (UV) Blockers/Fluorescing Aids / 6.6 6.5 Reinforcements / 6.6 6.5.1 Woven Fiberglass / 6.6 6.5.2 Yarn Nomenclature / 6.8 6.5.3 Fiberglass Scloths / 6.9 |     |

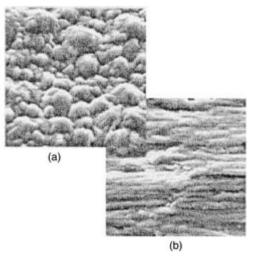

| <ul> <li>6.5.4 Other Reinforcements / 6.10</li> <li>6.6 Conductive Materials / 6.11</li> <li>6.6.1 Electrodeposited Copper Foil / 6.12</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 6.6.2 Reverse-Treated Foils / 6.14<br>6.6.3 Wrought Annealed Copper Foils / 6.15<br>6.6.4 Other Foil Types / 6.16<br>References / 6.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

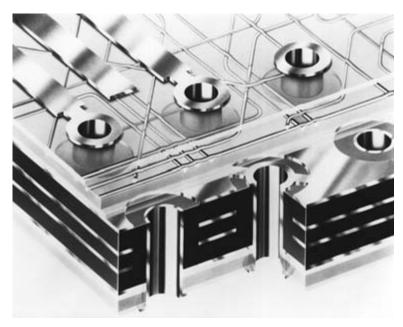

| Chapter 7. Base Material Manufacturing Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7.1 |

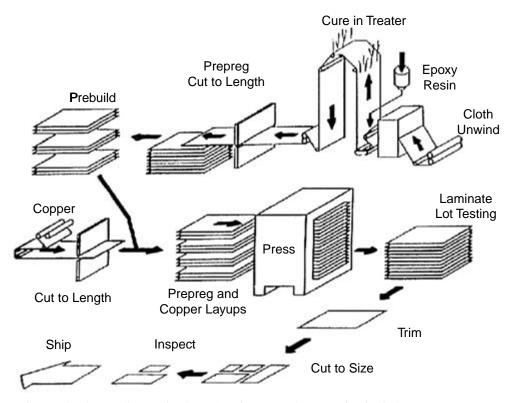

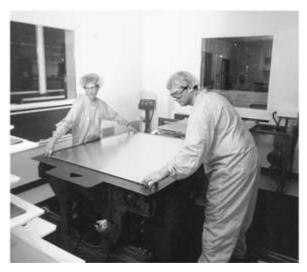

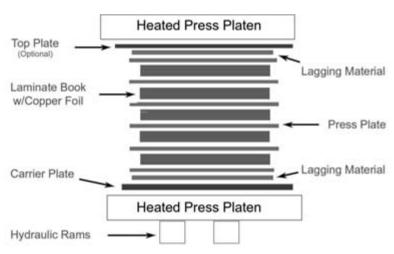

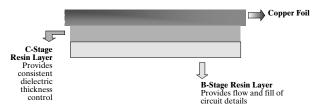

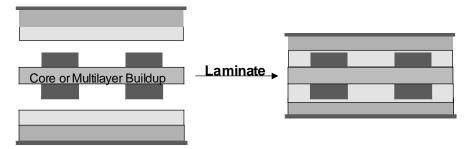

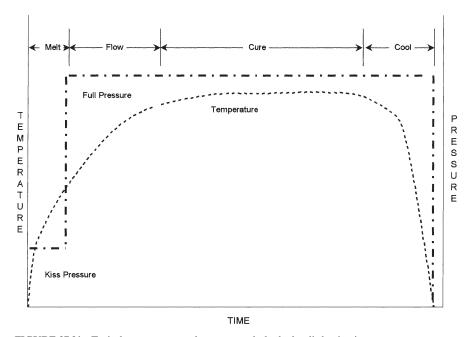

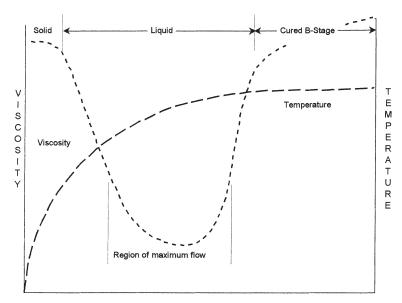

| <ul> <li>7.1 Laminate and Prepreg Manufacturing Processes / 7.1</li> <li>7.2 Conventional Manufacturing Processes / 7.1</li> <li>7.2.1 Prepreg Manufacturing / 7.1</li> <li>7.2.2 Laminate Manufacturing / 7.3</li> <li>7.3 Direct-Current or Continuous-Foil Manufacturing / 7.6</li> <li>7.4 Continuous Manufacturing Processes / 7.7</li> <li>References / 7.7</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Chapter 8. Properties of Base Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.1 |

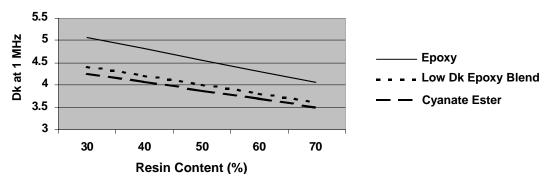

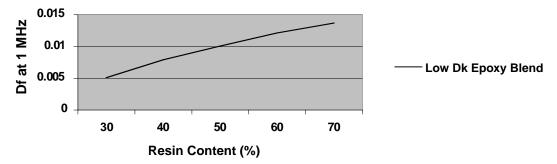

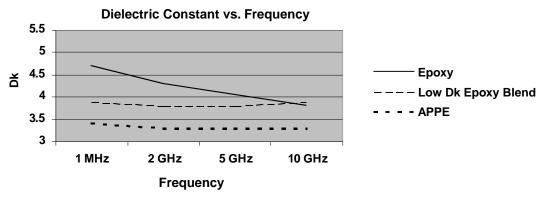

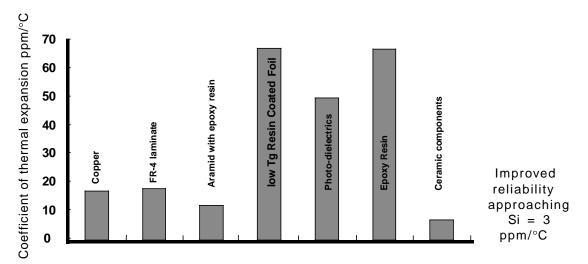

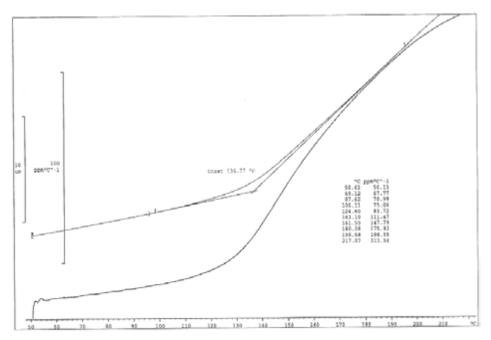

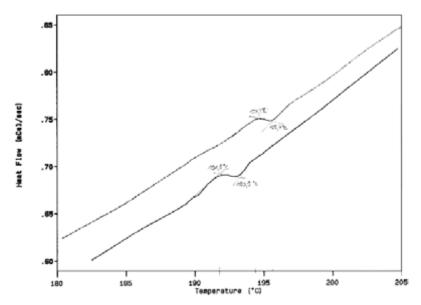

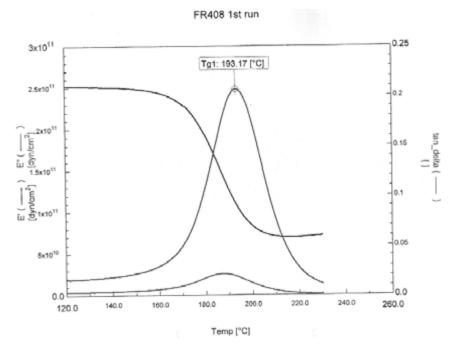

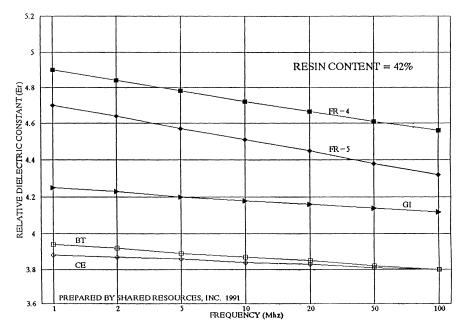

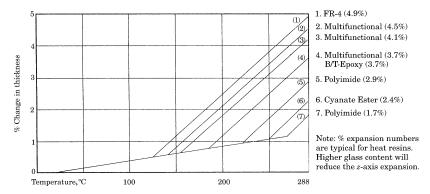

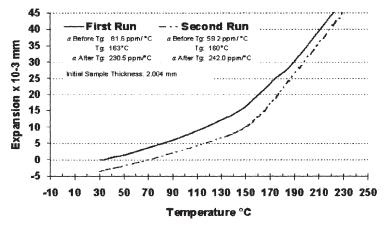

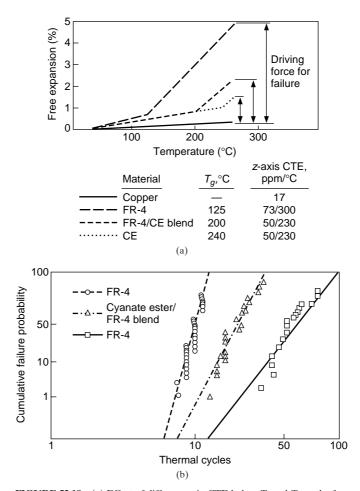

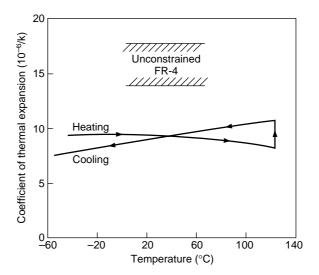

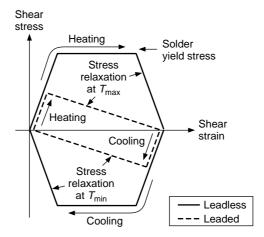

| <ul> <li>8.1 Introduction / 8.1</li> <li>8.2 Thermal, Physical, and Mechanical Properties / 8.1</li> <li>8.2.1 Coefficient of Thermal Expansion (CTE) / 8.1</li> <li>8.2.2 Time to Delamination / 8.3</li> <li>8.2.3 Decomposition Temperature / 8.3</li> <li>8.2.4 Arc Resistance / 8.3</li> <li>8.2.5 Density / 8.4</li> <li>8.2.6 Copper Peel Strength / 8.4</li> <li>8.2.7 Flexural Strength / 8.5</li> <li>8.2.8 Water and Moisture Absorption / 8.5</li> <li>8.2.9 Chemical Resistance / 8.6</li> <li>8.2.10 Flammability / 8.6</li> <li>8.3 Electrical Properties / 8.7</li> <li>8.3.1 Dielectric Constant or Permittivity / 8.7</li> <li>8.3.2 Dissipation Factor or Loss Tangent (Tan δ) / 8.8</li> <li>8.3.3 Insulation Resistance / 8.8</li> <li>8.3.4 Volume Resistivity / 8.8</li> <li>8.3.5 Surface Resistivity / 8.8</li> <li>8.3.6 Electrical Strength / 8.9</li> <li>8.3.7 Dielectric Breakdown / 8.9</li> <li>References / 8.9</li> </ul> |     |

| Chapter 9. Densification Issues for Base Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.1 |

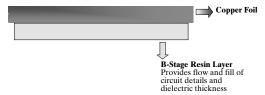

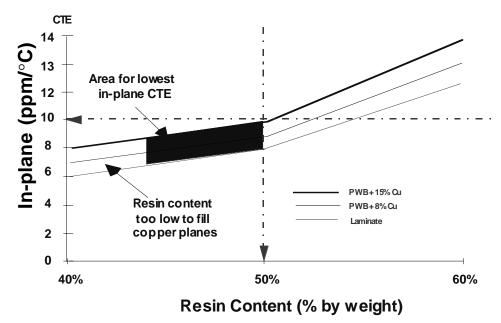

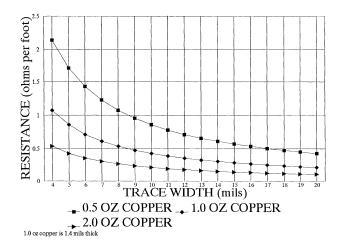

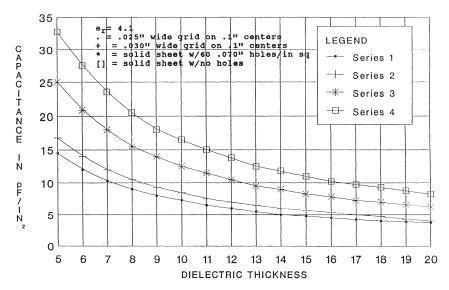

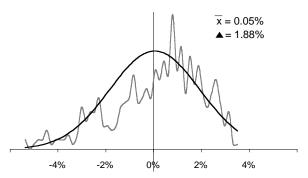

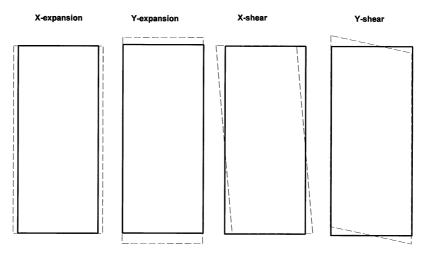

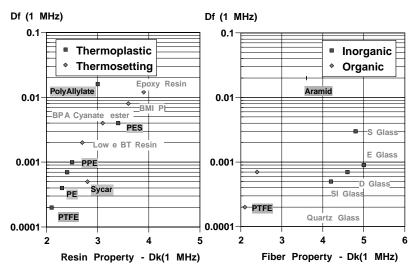

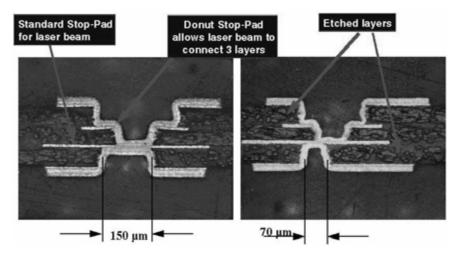

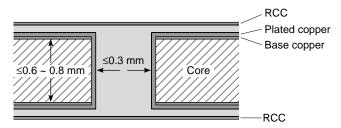

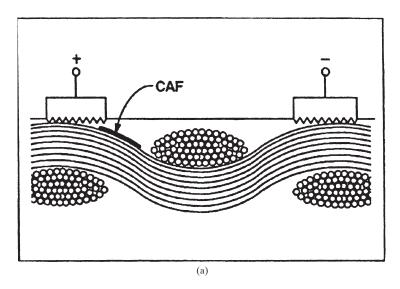

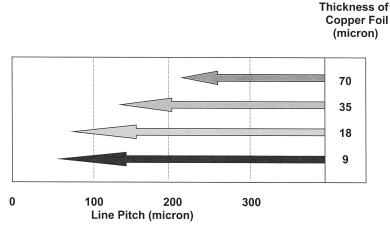

| 9.1 Impact of Trends in IC Technology and PCB Design / 9.1 9.2 Methods of Increasing Circuit Density / 9.2 9.3 Copper Foil / 9.2 9.3.1 HTE Foil / 9.2 9.3.2 Low-Profile and Reverse-Treated Copper Foils / 9.2 9.3.3 Thin Copper Foils / 9.3 9.3.4 Foils for High-Performance Resin Systems / 9.4 9.4 Dimensional Stability / 9.4 9.4.1 A Model of Printed Circuit Registration Capability / 9.4 9.4.2 Dimensional Stability Test Methods / 9.5 9.4.3 Improving Dimensional Stability / 9.5 9.5 Thermal Properties and Reliability / 9.6 9.5.1 Reliability Testing / 9.6 9.5.2 Conductive Anodic Filament (CAF) Growth / 9.7 9.5.3 Choosing a Base Material / 9.7 9.6 Electrical Properties / 9.8 9.6.1 Importance of These Properties / 9.8 9.6.2 Choosing a Base Material / 9.9 9.7 High-Density Interconnect/Microvia Materials / 9.12                                                                                                                   |     |

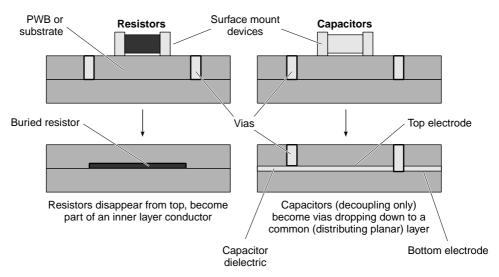

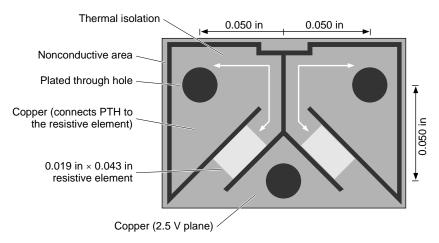

| 9.8 Integrated Passives / 9.13 9.8.1 Buried Capacitance / 9.13 9.8.2 Buried Resistors / 9.14 References / 9.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Chapter 10. Introducing Base Materials into the PCB Manufacturing Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10.    |

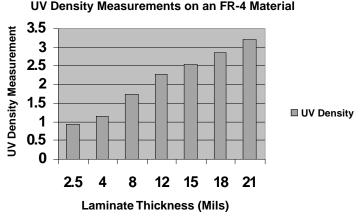

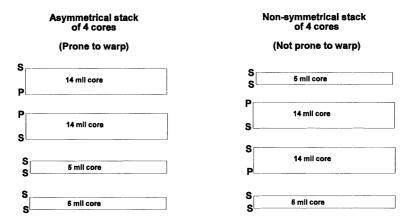

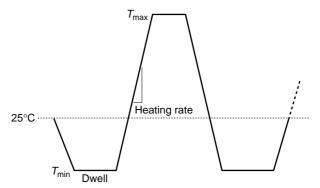

| <ul> <li>10.1 Introduction / 10.1</li> <li>10.2 Validation of Physical, Thermal, and Electrical Properties / 10.1</li> <li>10.3 Laminate Constructions / 10.2  10.3.1 Single-Ply vs. Multiple-Ply Constructions / 10.2  10.3.2 Resin Contents / 10.3  10.3.3 Laminate Flatness and Flexural Strength / 10.3  10.4 Prepreg Options and Yield per Ply Values / 10.3  10.5 Multilayer Press Cycle Qualification / 10.3  10.6 Prepreg-to-Innerlayer Circuit Adhesion / 10.5  10.7 Dimensional Stability Characterizations / 10.6  10.8 Impedance Characterizations / 10.6  10.9 Drilling Optimization / 10.6  10.10 Desmearing and Electroless Copper Deposition Characteristics / 10.8  10.11 Absorption of Ultraviolet Light / 10.9  10.12 Fluorescence at Automatic Optical Inspection / 10.9</li> <li>References / 10.10</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| Chapter 11. HDI Microvia Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11.    |

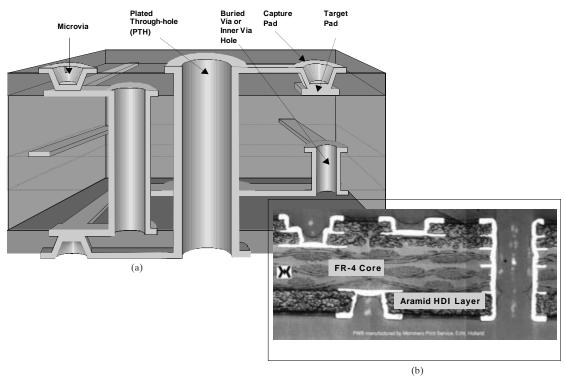

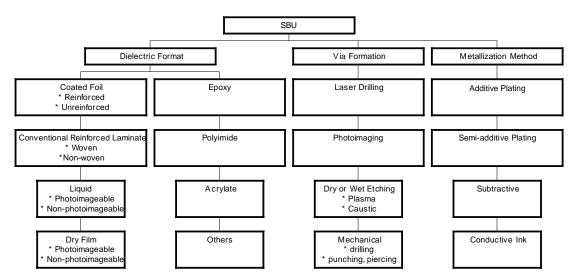

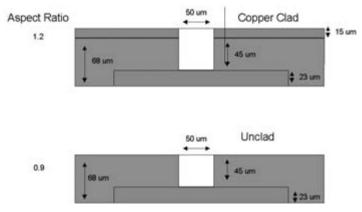

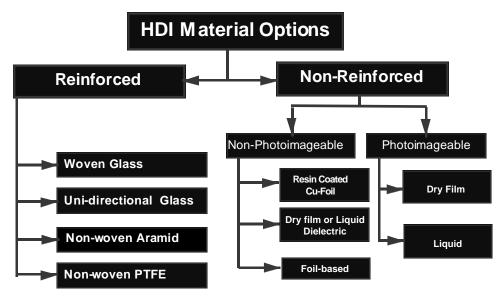

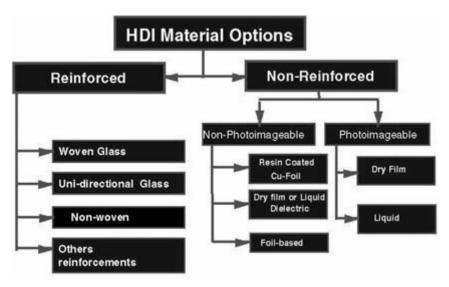

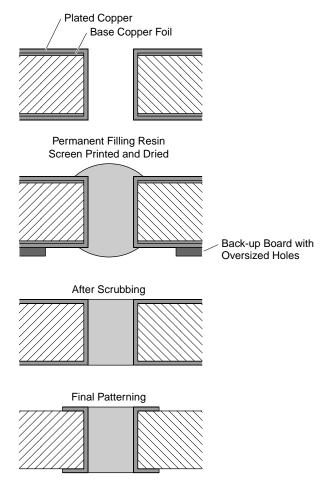

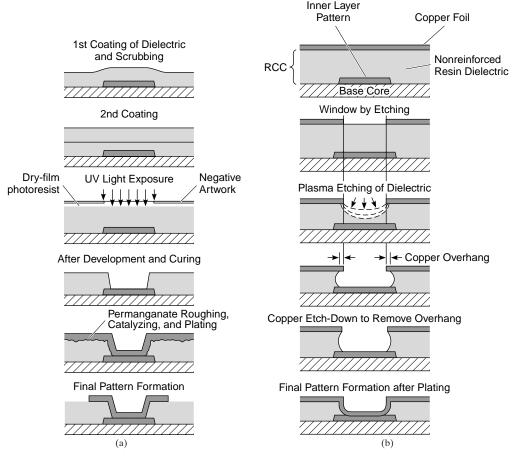

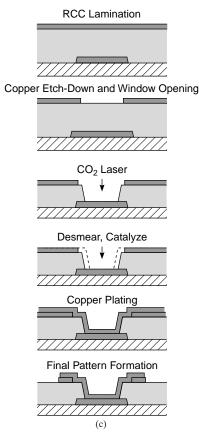

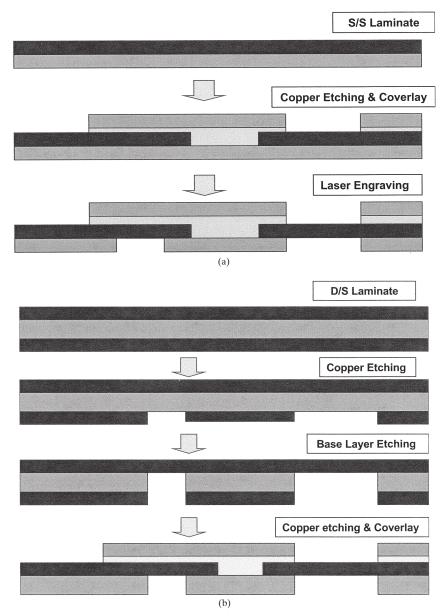

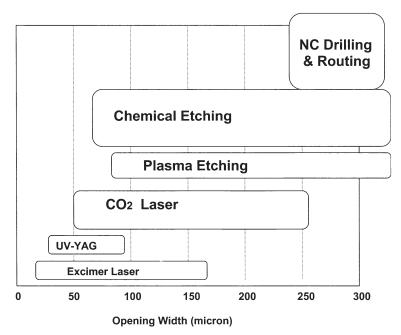

| <ul> <li>11.1 Introduction / 11.1</li> <li>11.2 Definitions / 11.1</li> <li>11.3 Technology Considerations for HDI Microvia Fabrication / 11.1</li> <li>11.3.1 Laser Via Formation / 11.2</li> <li>11.3.2 Etching-Process-Formed Vias / 11.3</li> <li>11.3.3 Photovia Formation / 11.4</li> <li>11.3.4 Dry Metallization (Conductive Inks/Conductive Paste/Insulation Displacement)</li> <li>11.4 Alternative HDI Constructions for Improved Area Utilization / 11.5</li> <li>11.4.1 ALIVH® / 11.5</li> <li>11.4.2 B²it / 011.6</li> <li>11.5 Materials for HDI Microvia Fabrication / 11.7</li> <li>11.5.1 Copper-Clad Dielectric Materials / 11.8</li> <li>11.5.2 Unclad Dielectric Materials / 11.8</li> <li>11.5.3 Clad vs. Unclad Dielectric Materials / 11.9</li> <li>11.6 Material and Technology Drivers / 11.10</li> <li>11.7 Examples of HDI Microvia Organic Substrates / 11.11</li> <li>11.7.1 Nonreinforced Dielectric Materials / 11.12</li> <li>11.7.2 Aramid-Reinforced, Nonwoven, Nonglass Laminate / 11.15</li> <li>11.8 Via Filling / 11.17</li> <li>11.8.1 Basics / 11.17</li> <li>11.8.2 Screen-Printed Via-Filling Materials / 11.18</li> <li>11.9 Acknowledgments / 11.19</li> <li>References / 11.20</li> </ul> | / 11.5 |

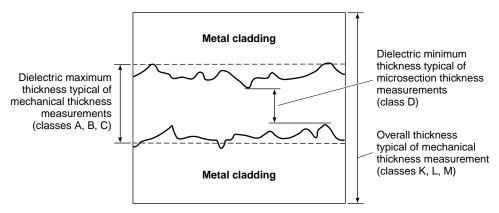

| Chapter 12. Laminate Qualification and Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.    |

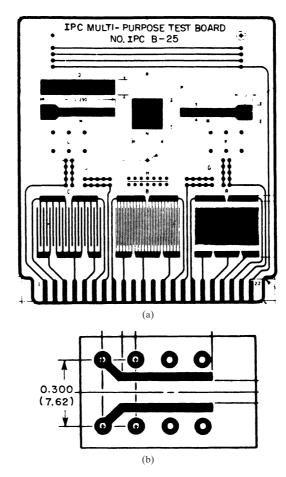

| 12.1 Introduction / 12.1 12.2 Industry Standards / 12.1 12.2.1 IPC-TM-650 / 12.2 12.2.2 IPC Specification Sheets / 12.2 12.2.3 American Society for Testing and Materials (ASTM) / 12.2 12.2.4 National Electrical Manufacturers Association (NEMA) / 12.2 12.2.5 NEMA Grades / 12.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| 12.3 Laminate Test Strategies / 12.3             |

|--------------------------------------------------|

| 12.3.1 Data Comparison / 12.4                    |

| 12.3.2 Two-Tier Strategy Approach / 12.4         |

| 12.4 Initial Tests / 12.4                        |

| 12.4.1 Surface and Appearance / 12.4             |

| 12.4.2 Copper Peel Strength / 12.5               |

| 12.4.3 Solder Shock / 12.6                       |

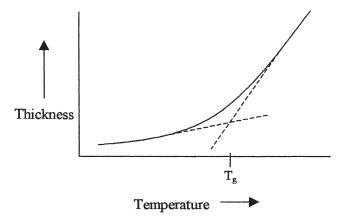

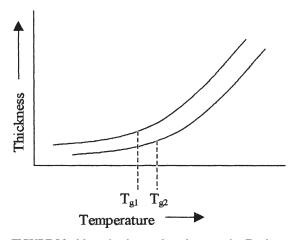

| 12.4.4 Glass Transition Temperature $T_g$ / 12.6 |

| 12.5 Full Material Characterization / 12.6       |

| 12.5.1 Mechanical Tests / 12.7                   |

| 12.5.2 Thermomechanical Tests / 12.9             |

| 12.5.3 Electrical Characterization / 12.16       |

| 12.5.4 Other Laminate Properties / 12.18         |

| 12.6 Characterization Test Plan / 12.19          |

| 12.7 Manufacturability in the Shop / 12.20       |

### Part 3 Engineering and Design

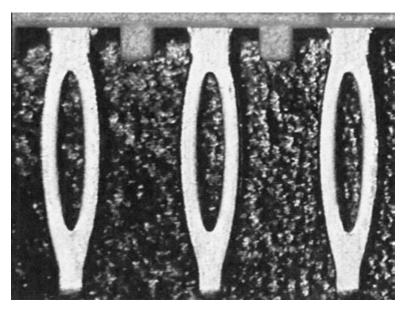

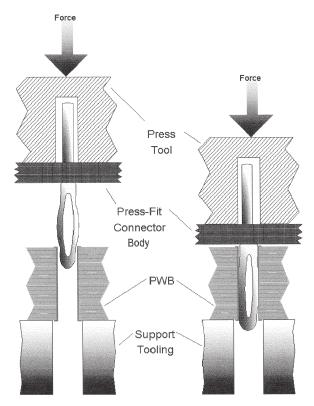

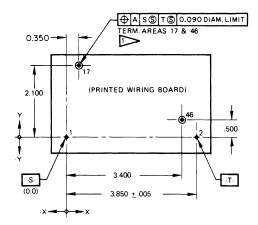

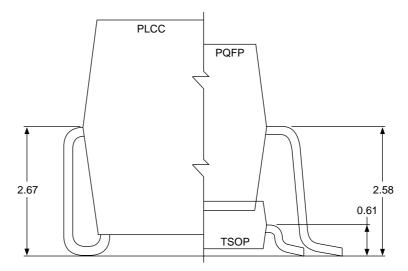

### Chapter 13. Physical Characteristics of PCB

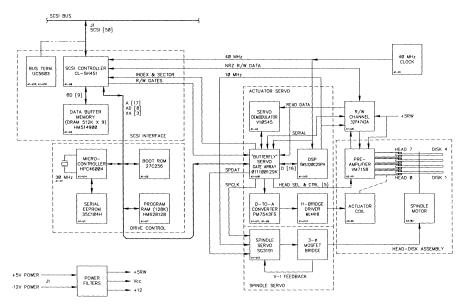

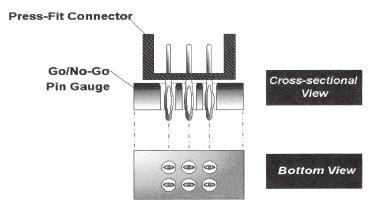

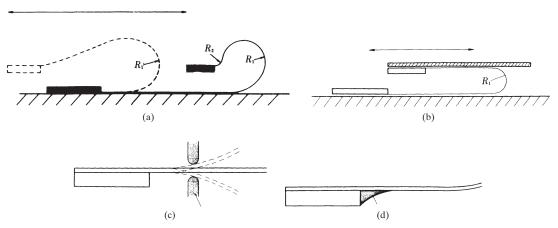

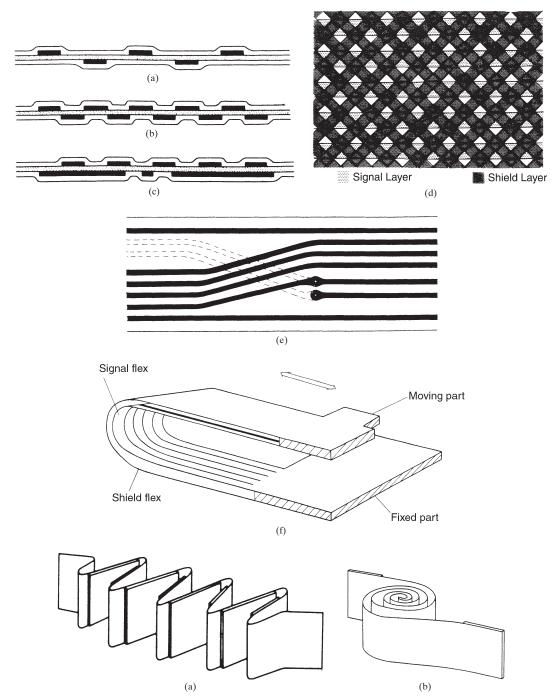

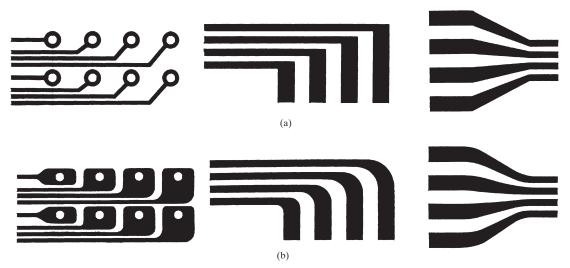

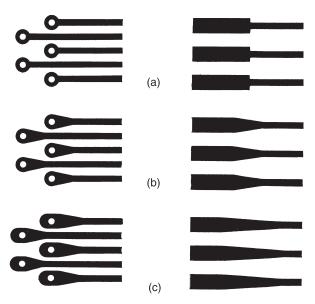

13.1 Classes of PCB Designs / 13.3 13.1.1 Characteristics of Analog, RF, and Microwave PCBs / 13.3 13.1.2 Characteristics of Digital-Based PCBs / 13.6 13.2 Types of PCBs or Packages for Electronic Circuits / 13.9 13.2.1 Single- and Double-Sided PCBs / 13.9 13.2.2 Multilayer PCBs / 13.10 13.2.3 Discrete-Wire or Multiwire PCBs / 13.10 13.2.4 Hybrids / 13.10 13.2.5 Flexible Circuits / 13.10 13.2.6 Flexible Rigid or Flex-Rigid / 13.12 13.2.7 Backplanes / 13.12 13.2.8 MCMs (Multichip Modules) / 13.12 13.3 Methods of Attaching Components / 13.14 13.3.1 Through-Hole Only / 13.14 13.3.2 Through-Hole Mixed with Surface-Mount / 13.14 13.3.3 Surface-Mount, One Side Only / 13.14 13.3.4 Surface-Mount, Both Sides / 13.14 13.3.5 Surface-Mount, Both Sides with Through-Hole / 13.14 13.4 Component Package Types / 13.15 13.4.1 Through-Hole / 13.15 13.4.2 Surface Mount / 13.15 13.4.3 Fine Pitch / 13.16 13.4.4 Press Fit / 13.16 13.4.5 TAB / 13.16 13.4.6 Flip Chip / 13.17 13.4.7 BGA / 13.17 13.4.8 Wire-Bonded Bare Die / 13.17 13.5 Materials Choices / 13.18 13.5.1 Reinforcement Materials / 13.19 13.5.2 Polyimide Resin Systems / 13.20 13.5.3 Epoxy-Based Resin Systems / 13.20 13.5.4 Cyanate Ester-Based Resin Systems / 13.20 13.5.5 Ceramics / 13.20 13.5.6 Exotic Laminates / 13.20 13.5.7 Embedded Components Materials / 13.21 13.6 Fabrication Methods / 13.22 13.6.1 Punch Forming / 13.22 13.6.2 Roll Forming / 13.22

| 13.7                 | 13.6.3 Lamination / 13.23<br>13.6.4 Subtractive Plating / 13.23<br>13.6.5 Additive Plating / 13.23<br>13.6.6 Discrete Wire / 13.23<br>Choosing a Package Type and Fabrication Vendor / 13.24<br>13.7.1 Trading Off Number of Layers Against Area / 13.24<br>13.7.2 One PCB vs. Multiple PCBs / 13.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Chap                 | oter 14. The PCB Design Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14.1 |

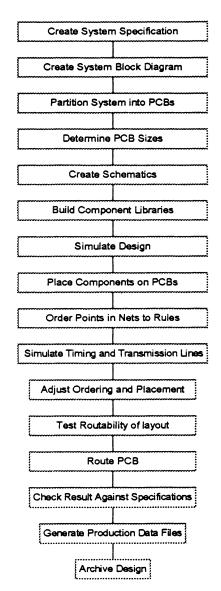

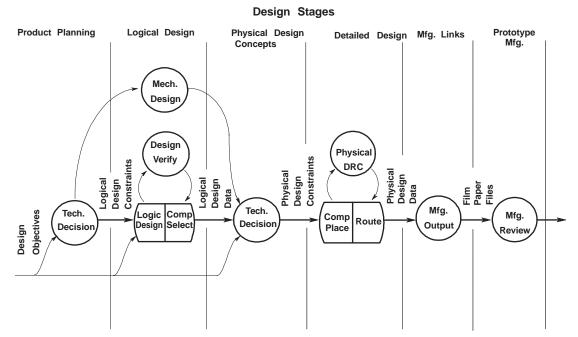

| 14.3<br>14.4         | Objective of the PCB Design Process / 14.1  Design Processes / 14.1  14.2.1 The System Specification / 14.1  14.2.2 System Block Diagram / 14.2  14.2.3 Partitioning System into PCBs / 14.2  14.2.4 Determining PCB Size / 14.2  14.2.5 Creating the Schematic / 14.2  14.2.6 Building Component Libraries / 14.3  14.2.7 Simulating Design / 14.3  14.2.9 Sequencing Nets to High-Speed Rules / 14.4  14.2.10 Simulating Timing and Transmission Lines Effects / 14.4  14.2.11 Adjusting Sequencing and Placement / 14.4  14.2.12 Testing Routability of Placement / 14.4  14.2.13 Routing PCB / 14.5  14.2.14 Checking Routed Results / 14.5  14.2.15 Generating Manufacturing Files / 14.5  14.2.16 Archiving Design / 14.5  Design Tools / 14.6  14.3.1 CAE Tools / 14.6  14.3.2 CAD Tools / 14.8  14.3.3 CAM Tools / 14.10  Selecting a Set of Design Tools / 14.10  14.4.1 Specification / 14.10  14.4.2 Supplier Survey / 14.11  14.4.3 Benchmarking / 14.11  14.4.4 Multiple Tools / 14.11  Interfacing CAE, CAD, and CAM Tools to Each Other / 14.11 |      |

| 14.6                 | Inputs to the Design Process / 14.11 14.6.1 Libraries / 14.11 14.6.2 PCB Characteristics / 14.12 14.6.3 Spacing and Width Rules / 14.12 14.6.4 Netlists / 14.12 14.6.5 Parts Lists / 14.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Chap                 | oter 15. Electrical and Mechanical Design Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15.1 |

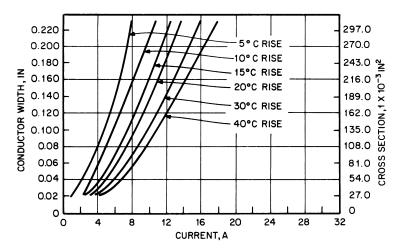

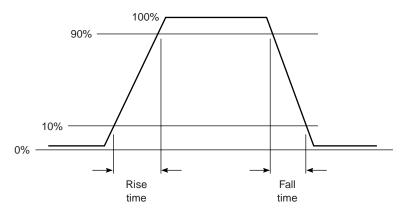

| 15.2<br>15.3<br>15.4 | Printed Circuit Design Requirements / 15.1 Introduction to Electrical Signal Integrity / 15.1 15.2.1 Drivers for Electrical Signal Integrity / 15.1 15.2.2 Analog Electrical Signal Integrity / 15.2 15.2.3 Digital Electrical Signal Integrity / 15.3 Introduction to Electromagnetic Compatibility / 15.3 Noise Budget / 15.4 Designing for Signal Integrity and Electromagnetic Compatibility / 15.4 15.5.1 High Speed and High Frequency / 15.4 15.5.2 Leakage Currents and Voltages / 15.5 15.5.3 Voltage and Ground Distribution Concepts / 15.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

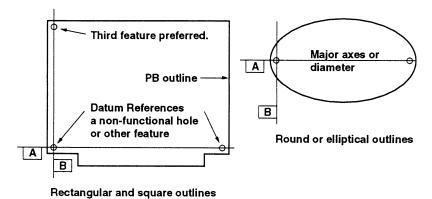

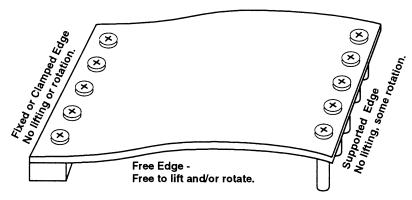

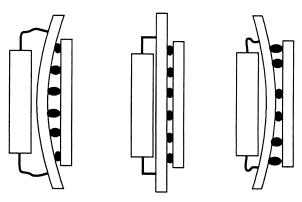

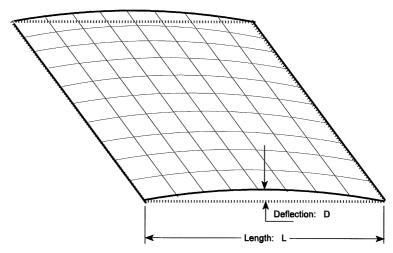

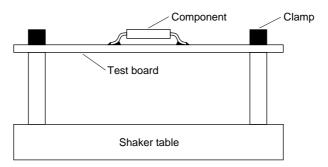

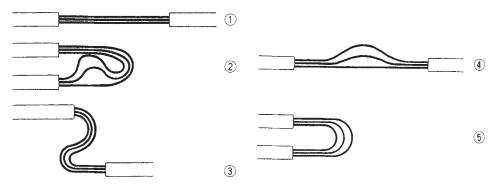

| 15.6 Mechanical Design Requirements / 15.9 15.6.1 General Mechanical Design Requirements / 15.10 15.6.2 Shock and Vibration / 015.12 15.6.3 Methods of Reinforcement and Snubbers / 15.17 References / 15.17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

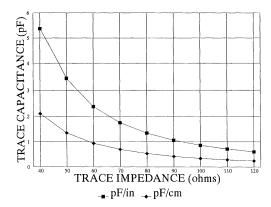

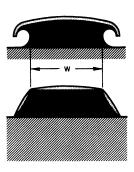

| Chapter 16. Controlled Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16.1 |

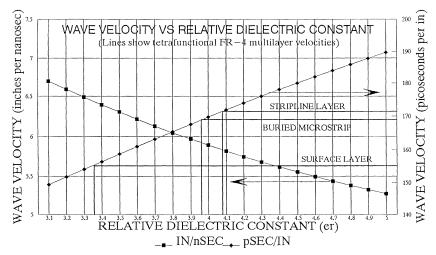

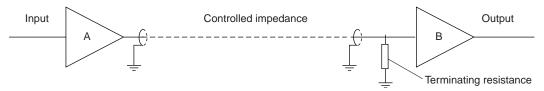

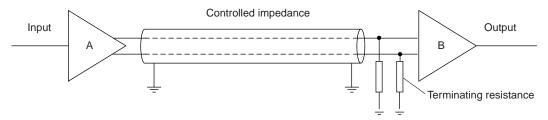

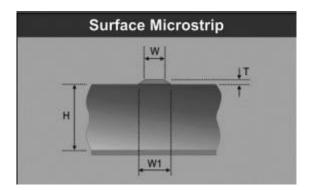

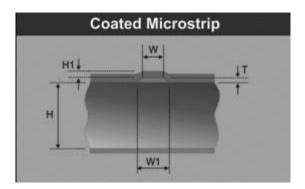

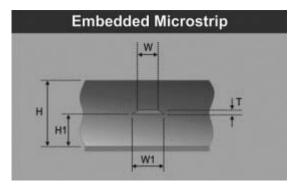

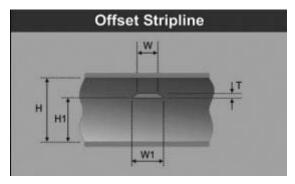

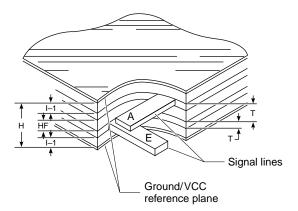

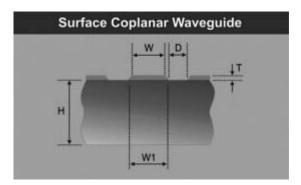

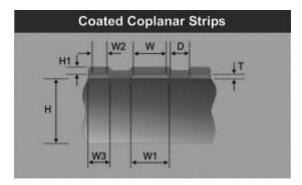

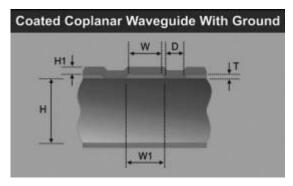

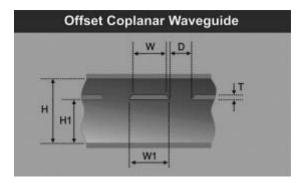

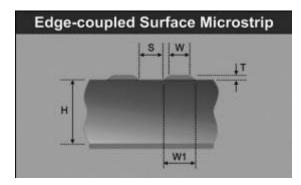

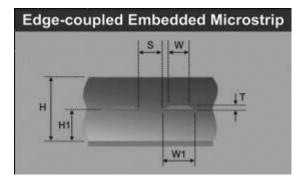

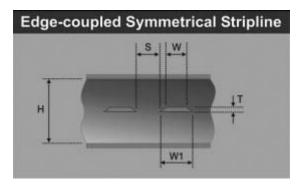

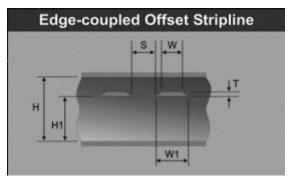

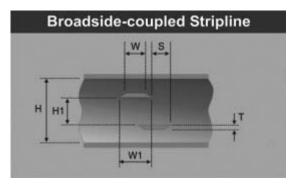

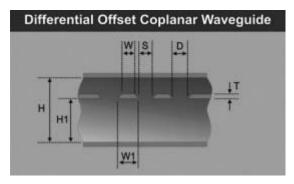

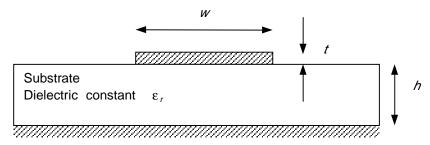

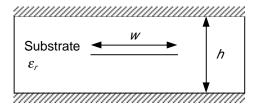

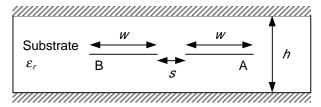

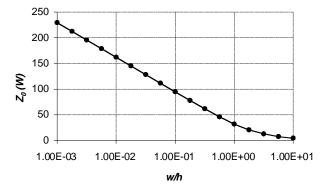

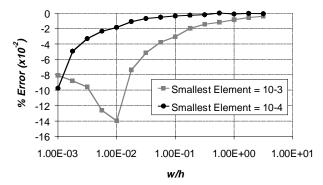

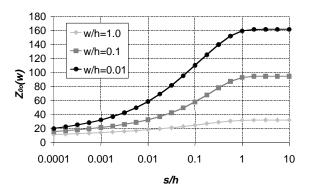

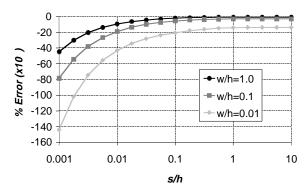

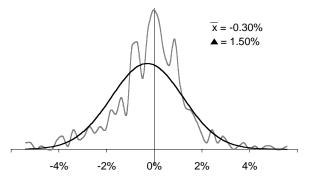

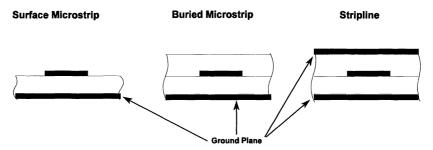

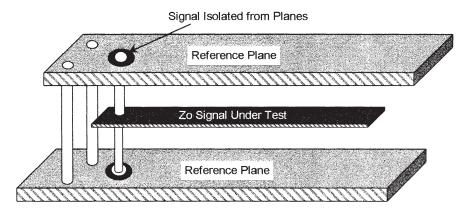

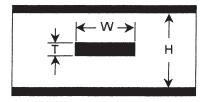

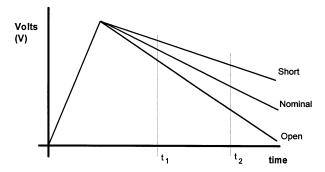

| 16.1 Introduction / 16.1 16.1.1 Definitions / 16.1 16.1.2 The Digital Signal (Pulse) / 16.1 16.1.3 Controlled-Impedance Needs / 16.2 16.2 Basic Impedance Mismatch Effects / 16.3 16.2.1 Signal Reflection Process / 16.3 16.2.2 Effect of Signal Frequency / 16.3 16.2.3 Effect of Components on Circuit Consistency / 16.4 16.3 Impedance / 16.4 16.3.1 Factors Determining Impedance / 16.4 16.3.2 Characteristic Impedance / 16.5 16.4 Transmission Lines / 16.5 16.4.1 Single-Ended Transmission Line / 16.5 16.4.2 Differential Transmission Line / 16.5 16.5 Transmission Line Implementation in a PCB / 16.6 16.5.1 Dimensions / 16.6 16.5.2 Factors of Influence / 16.7 16.5.3 Single-Ended Examples / 16.8 16.5.4 Differential Examples / 16.11 16.6 Calculation of PCB Track Impedance / 16.15 16.6.1 Microstrip Example / 16.15 16.6.2 Algebraic Equations / 16.17 16.6.3 Numerical Principles / 16.18 16.6.4 Numerical Results / 16.20 16.6.5 Practical Results / 16.22 16.7 Results Discussion / 16.22 16.8 Use of Personal Computers for Calculations / 16.23 References / 16.24 |      |

| Chapter 17. Multilayer Design Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17.1 |

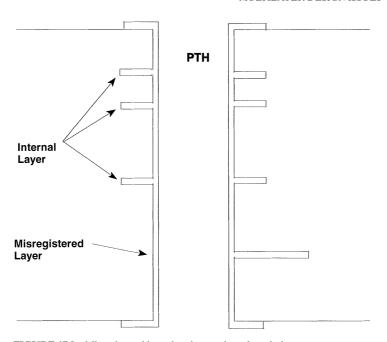

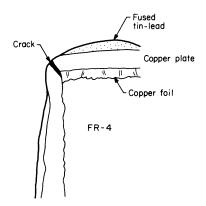

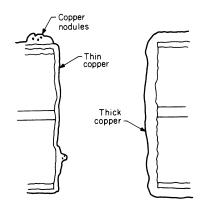

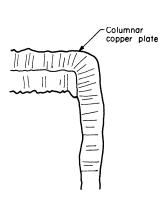

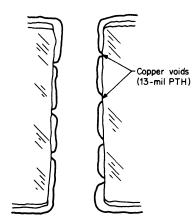

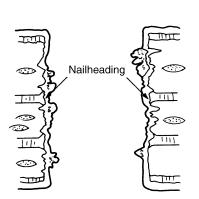

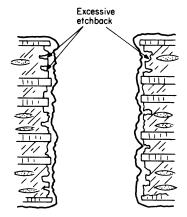

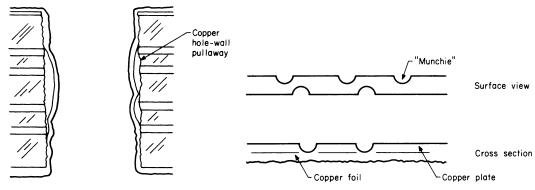

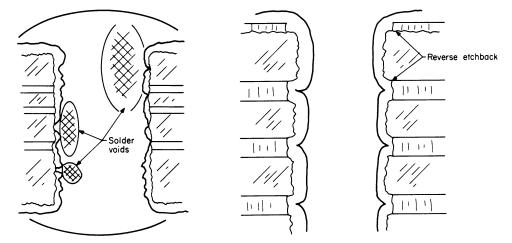

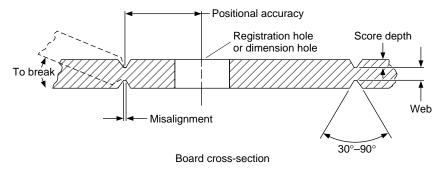

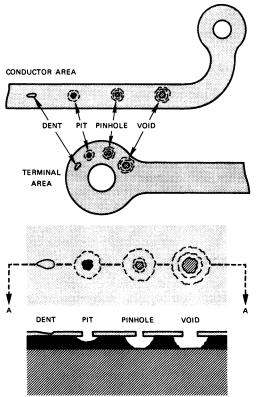

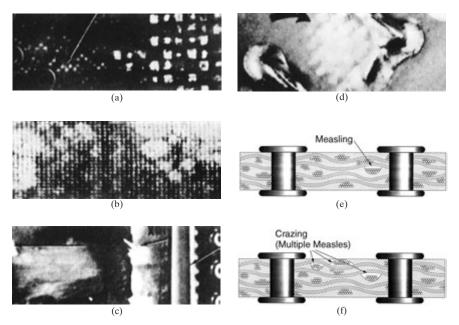

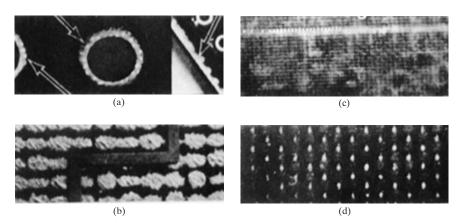

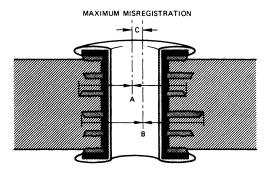

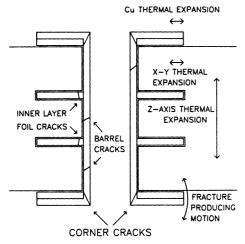

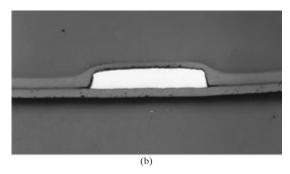

| 17.1 Reliability Issues / 17.1 17.1.1 Substrate Flaws / 17.2 17.1.2 Copper Surface Damage / 17.5 17.1.3 Mechanical Problems / 17.6 17.1.4 Internal Misregistration / 17.9 17.1.5 Connection Flaws / 17.16 17.2 Electrical Performance / 17.18 17.2.1 Controlled Impedance (CI) / 17.19 17.2.2 Signal Attenuation at High Frequency / 17.19 17.2.3 Signal Coupling at High Frequencies / 17.20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Chapter 18. Planning for Design, Fabrication, and Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18.1 |

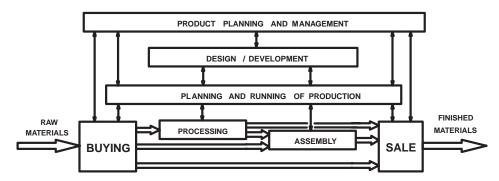

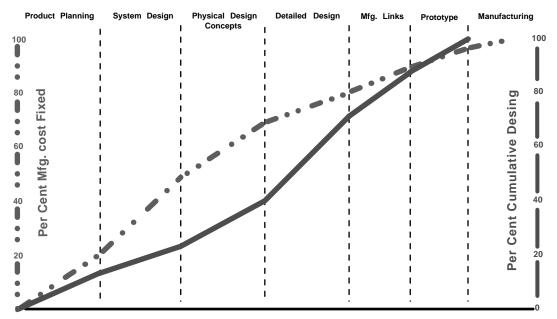

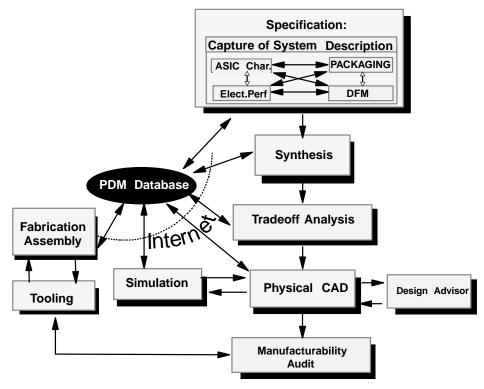

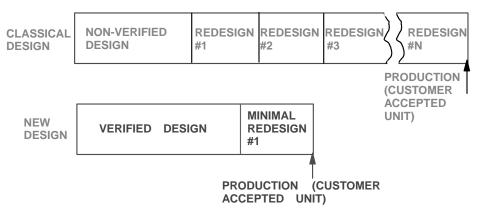

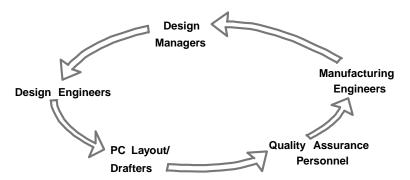

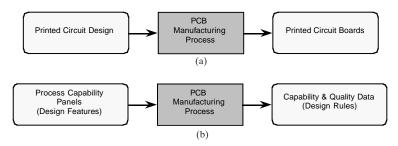

| 18.1 Introduction / 18.1  18.1.1 Design Planning and Predicting Cost / 18.1  18.1.2 Design Planning and Manufacturing Planning / 18.2  18.2 General Considerations / 18.2  18.2.1 Planning Elements / 18.2  18.2.2 Planning Concepts / 18.3  18.2.3 Producibility / 18.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

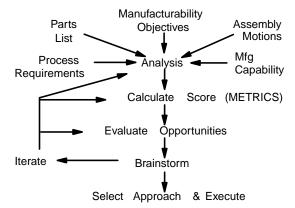

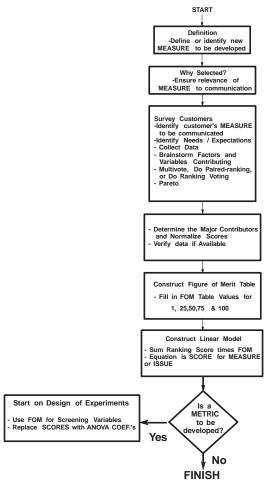

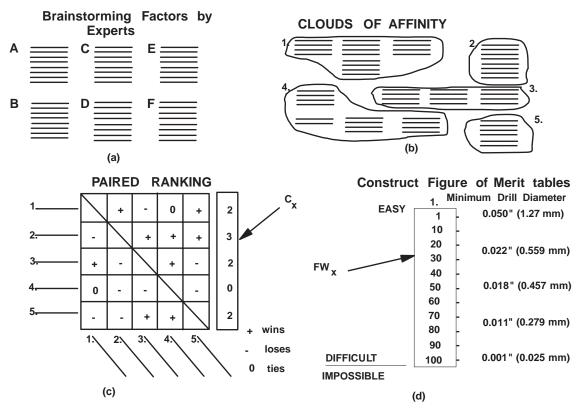

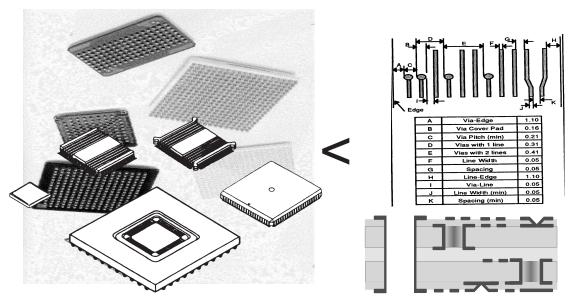

|      | New Product Design / 18.4  18.3.1 Expanded Design Process / 18.4  18.3.2 Product Definition / 18.4  18.3.3 Metrics for Predicting and Planning Producibility / 18.6  18.3.4 Nonmetrics / 18.7  18.3.5 Figure of Merit (FOM) Metric / 18.8  18.3.6 Figure of Merit Linear Equation / 18.9  Layout Trade-Off Planning / 18.11  18.4.1 Balancing the Density Equation / 18.11 |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 18.4.2 Wiring Demand $W_d$ / 18.12<br>18.4.3 Wiring Capacity $W_c$ / 18.13<br>18.4.4 Layout Efficiency / 18.13<br>18.4.5 Selecting Design Rules / 18.14<br>18.4.6 Typical Example of Wiring Demand Calculation / 18.18                                                                                                                                                     |     |

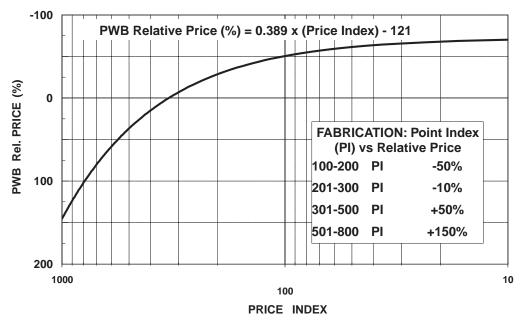

| 18.5 | PWB Fabrication Trade-Off Planning / 18.18 18.5.1 Fabrication Complexity Matrix / 18.18 18.5.2 Predicting Producibility / 18.19 18.5.3 Example of a Complete PWB Complexity Matrix / 18.21                                                                                                                                                                                 |     |

|      | Assembly Trade-Off Planning / 18.23<br>18.6.1 Assembly Complexity Matrix / 18.23<br>18.6.2 Example of an Assembly Complexity Matrix / 18.24                                                                                                                                                                                                                                |     |

|      | Tools for Audits / 18.25<br>18.7.1 Manufacturability Audits Performed by the Designer / 18.25<br>tences / 18.28                                                                                                                                                                                                                                                            |     |

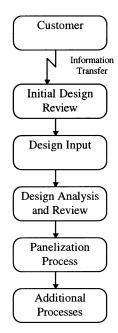

| Chap | oter 19. Manufacturing Information Documentation and Transfer                                                                                                                                                                                                                                                                                                              | 19. |

|      | Introduction / 19.1<br>Information Transfer / 19.1<br>19.2.1 Information Required / 19.2<br>19.2.2 Modem Transmission / 19.3<br>19.2.3 Internet Transmission / 19.3                                                                                                                                                                                                        |     |

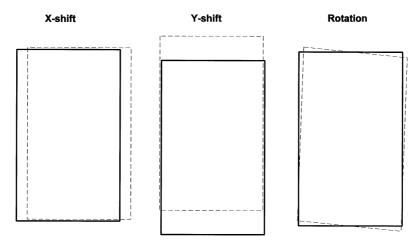

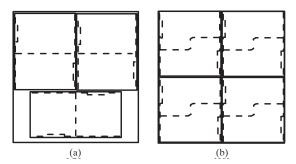

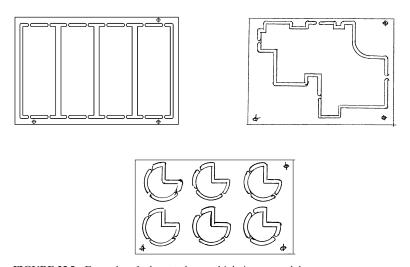

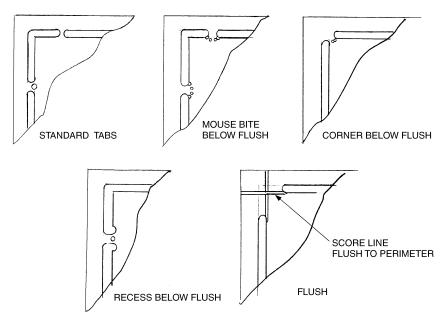

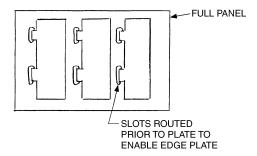

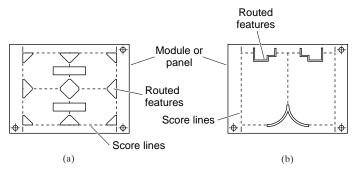

| 19.3 | Initial Design Review / 19.4<br>19.3.1 Design Review / 19.4<br>19.3.2 Material Requirements / 19.6<br>19.3.3 Process Requirements / 19.7<br>19.3.4 Panelization / 19.9                                                                                                                                                                                                     |     |

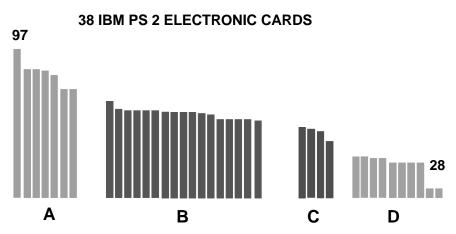

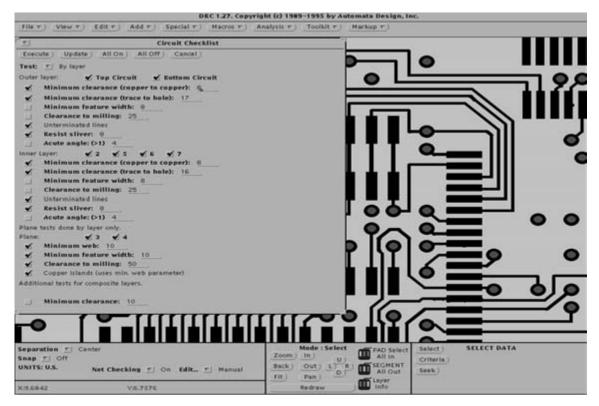

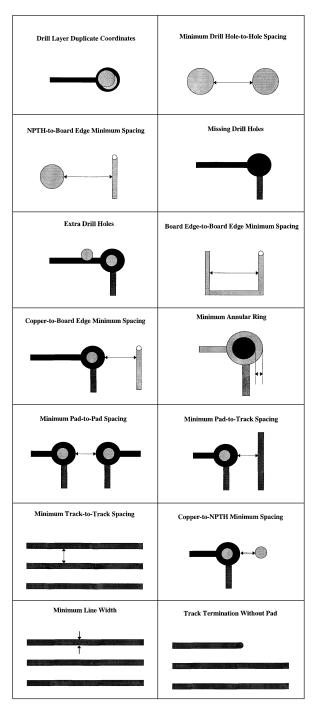

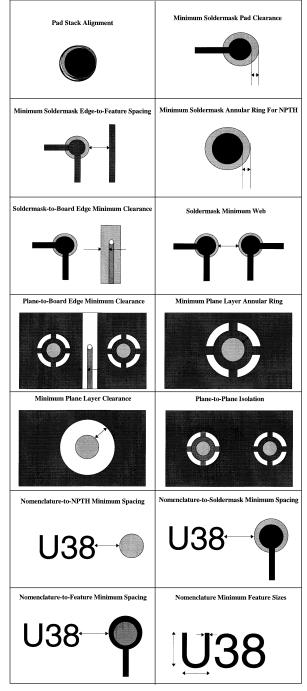

|      | 19.3.5 Initial Design Analysis / 19.10 Design Input / 19.11 Design Analysis and Review / 19.11 19.5.1 Design Rule Checking / 19.11 19.5.2 Manufacturability Review / 19.16 19.5.3 Single Image Edits / 19.16 19.5.4 DFM Enhancements / 19.16                                                                                                                               |     |

|      | Panelization Process / 19.18<br>Additional Processes / 19.18                                                                                                                                                                                                                                                                                                               |     |

|      | oter 20. Electronic Contract Manufacturing Supplier Selection<br>Management                                                                                                                                                                                                                                                                                                | 20. |

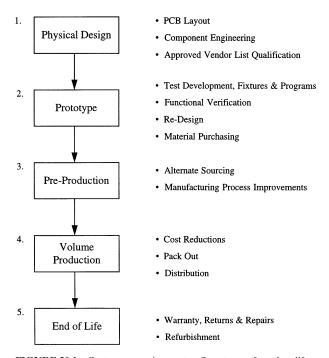

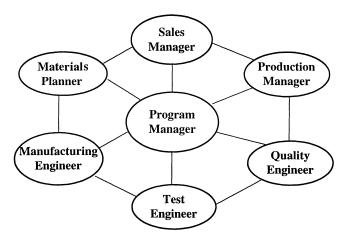

| 20.2 | Introduction / 20.1  20.1.1 Development of the Electronic Manufacturing Services Industry / 20.1  Business Plan / 20.2  20.2.1 Customer Requirements—Five Stages of Product Life / 20.2  20.2.2 Supplier Requirements / 20.3  20.2.3 Presenting the Corporate Goals and Objectives / 20.3  20.2.4 Business Plan / 20.4  Supplier Capabilities / 20.4                       |     |

| 20.3 | 20.3.1 Overall Capabilities / 20.4                                                                                                                                                                                                                                                                                                                                         |     |

|       | 20.3.2 Services Offered / 20.5<br>20.3.3 Support Services / 20.6                                                           |      |

|-------|----------------------------------------------------------------------------------------------------------------------------|------|

|       | 20.3.4 Technical Capability / 20.7                                                                                         |      |

|       | Supplier Qualification / 20.8                                                                                              |      |

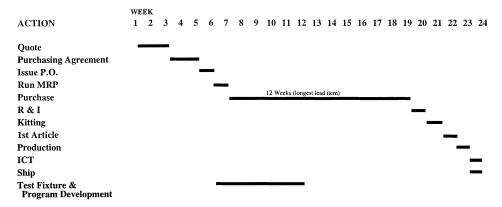

| 20.5  | Time-to-Market Elements / 20.8                                                                                             |      |

| 20.6  | 20.5.1 Specific Elements: Descriptions and Time Requirements / 20.8 Quality System / 20.11                                 |      |

| 20.0  | 20.6.1 Total Quality Management / 20.11                                                                                    |      |

|       | 20.6.2 ISO 9000 / 20.11                                                                                                    |      |

| 20.7  | Request for Quotation / 20.11                                                                                              |      |

|       | 20.7.1 Purpose / 20.11                                                                                                     |      |

|       | 20.7.2 Contents and Sample / 20.11                                                                                         |      |

| 20.8  | 20.7.3 Responses Required / 20.13 Managing the Relationship / 20.13                                                        |      |

| 20.0  | 20.8.1 Getting Started / 20.13                                                                                             |      |

|       | 20.8.2 Evaluating Performance: Customer Satisfaction Survey (CSS) / 20.15                                                  |      |

|       |                                                                                                                            |      |

| Par   | t 4 High-Density Interconnect                                                                                              |      |

| Chap  | oter 21. Introduction to High-Density Interconnection Technology                                                           | 21.3 |

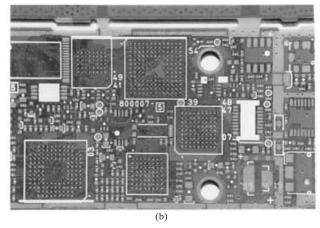

| 21.1  | High-Density Interconnects (HDIs) Defined / 21.3                                                                           |      |

|       | 21.1.1 HDI Characterization / 21.3                                                                                         |      |

|       | 21.1.2 Advantages and Benefits / 21.4                                                                                      |      |

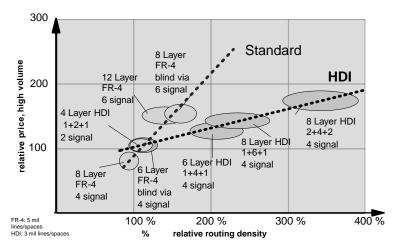

|       | 21.1.3 Comparison of HDIs and Traditional Printed Wiring Boards / 21.5<br>21.1.4 Design/Cost/Performance Trade-offs / 21.5 |      |

|       | 21.1.5 Specifications and Standards / 21.6                                                                                 |      |

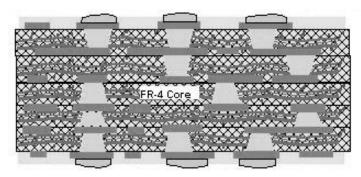

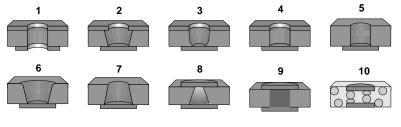

| 21.2  | HDI Structures / 21.6                                                                                                      |      |

|       | 21.2.1 Construction Types / 21.8                                                                                           |      |

|       | 21.2.2 Design Rules and Categories / 21.9                                                                                  |      |

| 21.3  | Design of HDI Boards / 21.10                                                                                               |      |

|       | 21.3.1 Design Tools / 21.11<br>21.3.2 Trade-off Analysis / 21.11                                                           |      |

| 21.4  | Materials / 21.12                                                                                                          |      |

| 21.1  | 21.4.1 HDI Material Requirements / 21.12                                                                                   |      |

|       | 21.4.2 Copper-Clad Dielectrics / 21.13                                                                                     |      |

|       | 21.4.3 Unclad Nonreinforced Dielectric / 21.16                                                                             |      |

| Refer | rences / 21.17                                                                                                             |      |

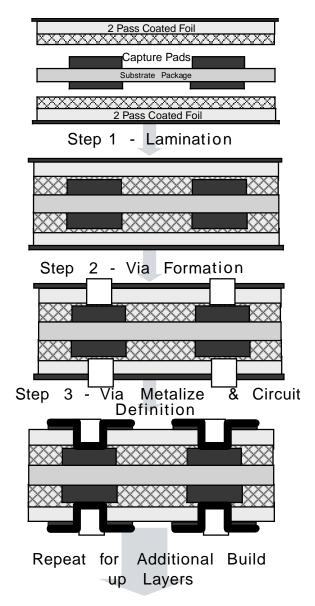

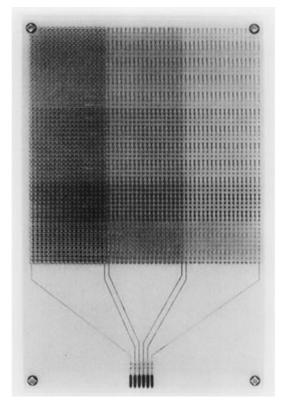

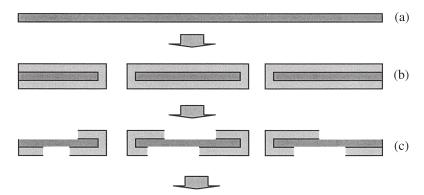

| Chap  | oter 22. High-Density Interconnect-Build-up Technologies                                                                   | 22.1 |

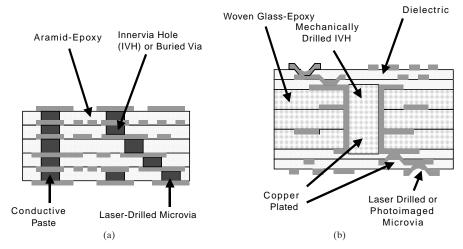

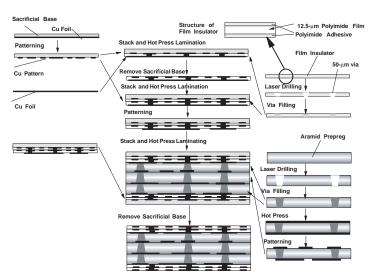

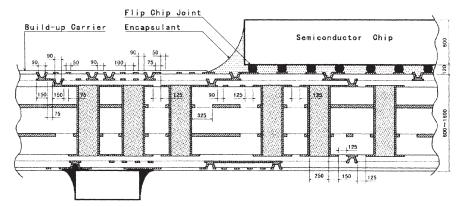

| 22.1  | Introduction to High-Density Interconnect Substrates / 22.1                                                                |      |

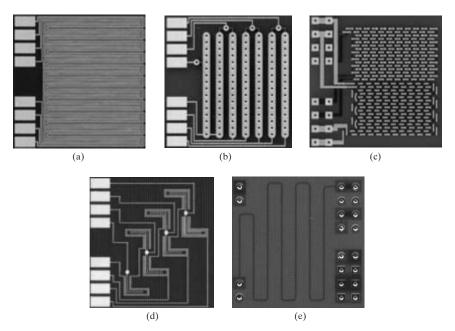

|       | Build-up Technologies / 22.1                                                                                               |      |

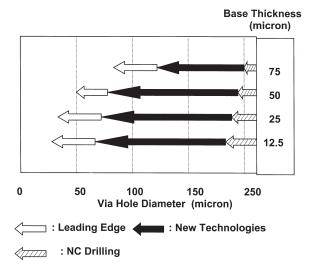

|       | 22.2.1 Mechanical Drilling / 22.2                                                                                          |      |

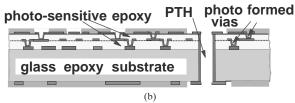

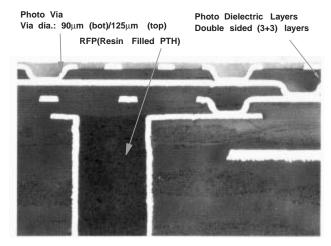

|       | 22.2.2 Photosensitive Dielectrics / 22.2                                                                                   |      |

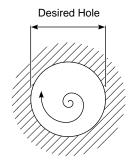

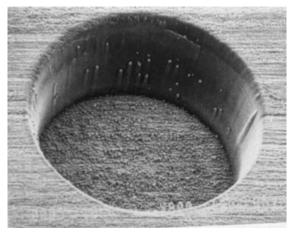

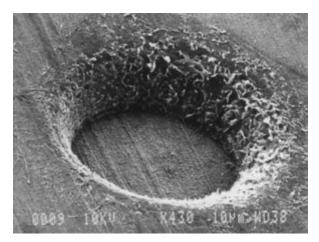

|       | 22.2.3 Laser Drilling / 22.4                                                                                               |      |

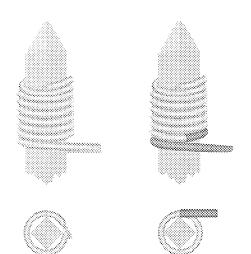

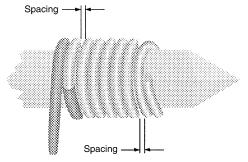

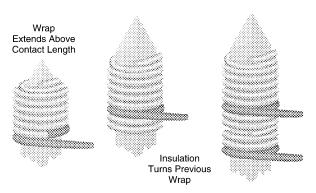

|       | 22.2.4 Plasma Etching / 22.5<br>22.2.5 Insulation Displacement / 22.5                                                      |      |

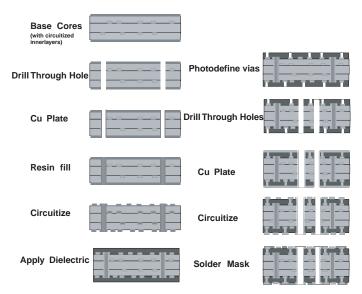

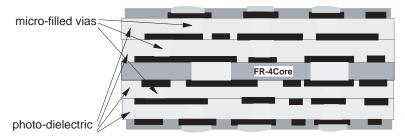

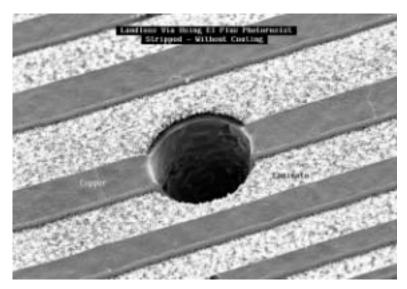

| 22.3  | Photodefined Via Technologies / 22.6                                                                                       |      |

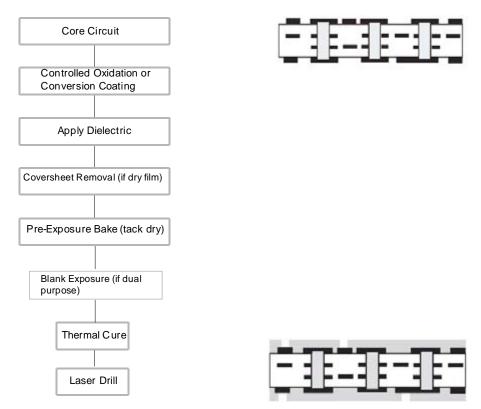

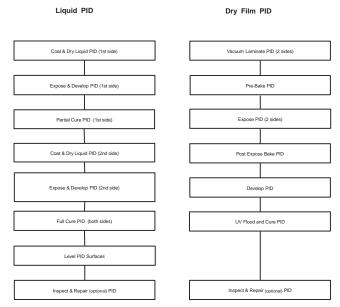

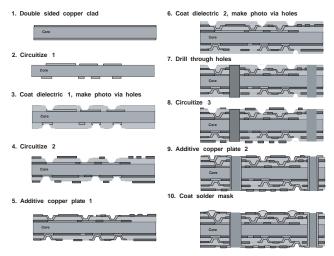

| 22.0  | 22.3.1 Photoimageable Dielectric Technology / 22.6                                                                         |      |

|       | 22.3.2 IPN Polymer Build-up Structure System / 22.9                                                                        |      |

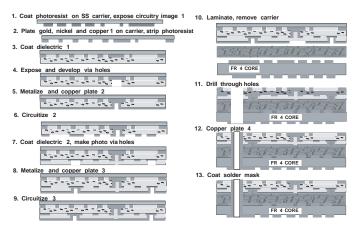

|       | 22.3.3 Carrier-Formed Circuits / 22.9                                                                                      |      |

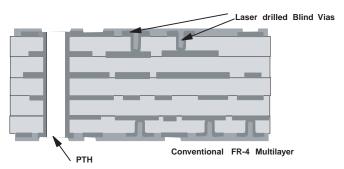

| 22.4  | Laser-Generated Vias / 22.10                                                                                               |      |

|       | 22.4.1 Laser-Formed Blind/Through-Vias / 22.10                                                                             |      |

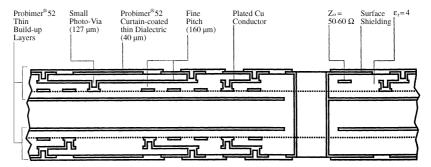

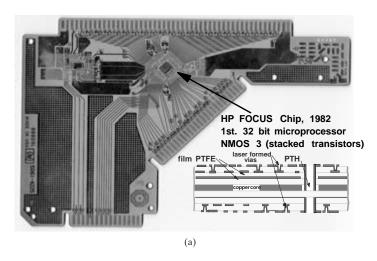

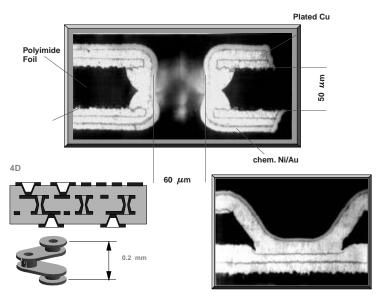

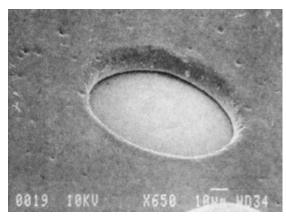

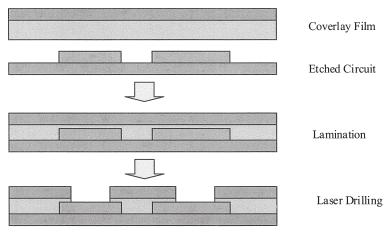

|       | 22.4.2 Laser-Drilled Flex (ViaThin) / 22.11 22.4.3 High-Density Interconnects / 22.12                                      |      |

| 22.5  | Chemical/Metallurgical Bonded Via in PWB Technologies / 22.13                                                              |      |

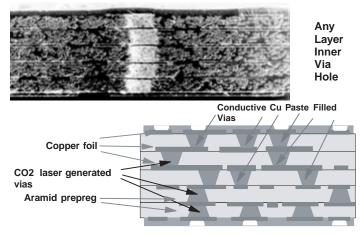

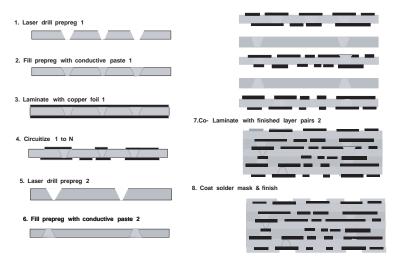

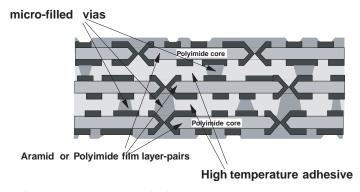

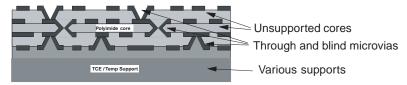

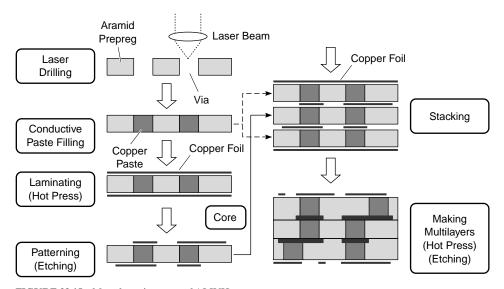

|       | 22.5.1 Paste-Bonded Solid-Via Laminate (ALIVH) / 22.13                                                                     |      |

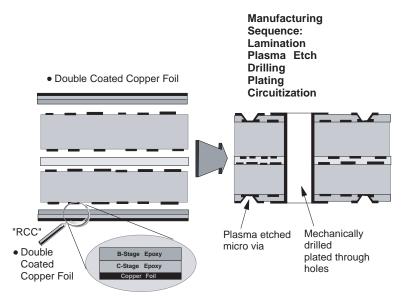

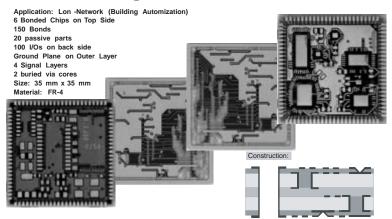

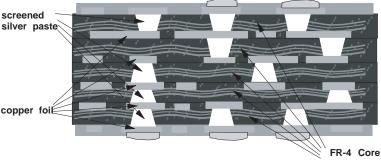

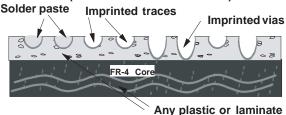

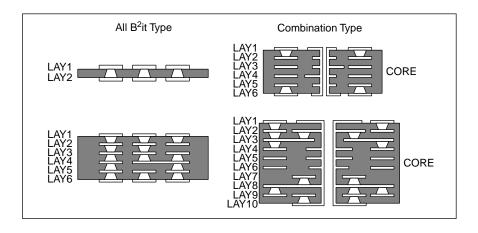

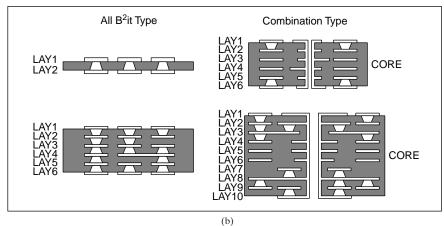

| 22.5.2 Co-lamination with Conductive Paste/Adhesive Structures / 22.14 22.5.3 Microfilled Via Technology (MfVia®) / 22.16 22.5.4 Transient Liquid Phase Sintering (TLPS) Conductive Circuits / 22.17 22.6 Wet/Dry-Etched Vias / 22.18 22.6.1 DYCOstrate / 22.18 22.6.2 Plasma-Etched Redistribution Layers (PERL) / 22.20 22.7 Insulation Displacement Technology / 22.22 22.7.1 Buried Bump Interconnect (BbiT) / 22.22 22.8 Imprinted Circuits / 22.23 References / 22.23                                                                                                                               |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Chapter 23. Microvia Hole Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23.1 |

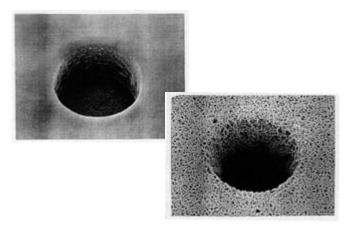

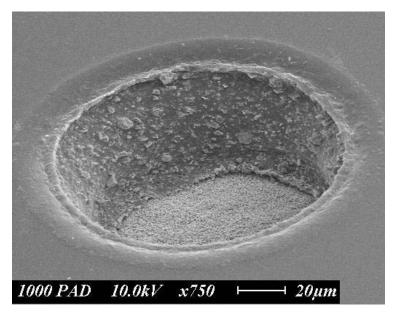

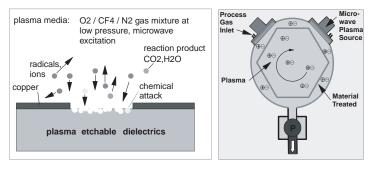

| 23.1 Introduction / 23.1 23.2 Definitions / 23.1 23.3 Dielectric Materials and Coating Methods / 23.3 23.4 Photovia Materials / 23.4 23.5 Laser Via Materials / 23.4 23.6 Plasma Via Materials / 23.6 23.7 Paste Via Materials / 23.6 23.8 Manufacturing Processes / 23.6 23.8.1 Photovia Process / 23.7 23.8.2 Plasma Via Process / 23.8 23.8.3 Laser Via Process / 23.9 23.9 Multiple Layers of Microvia Holes / 23.12 23.10 Other Microvia Technologies / 23.13 23.10.1 ALIVH / 23.13 23.10.2 B <sup>2</sup> it / 23.14 23.10.3 Other Microvia Processes / 23.15 References / 23.15 References / 23.15 |      |

| Part 5 Fabrication Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

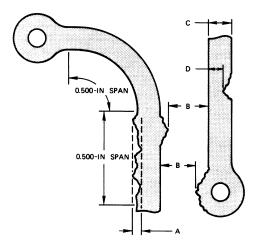

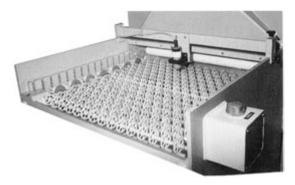

| Chapter 24. Drilling Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24.3 |

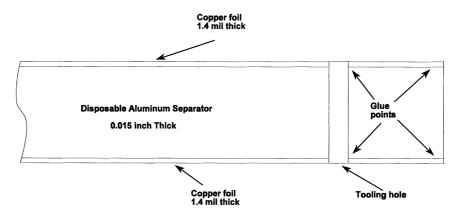

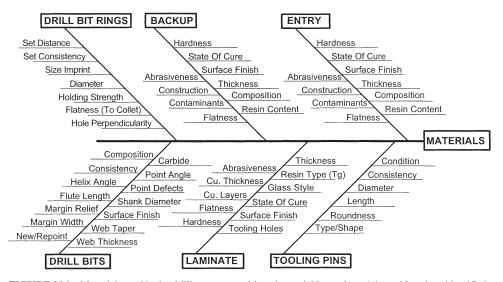

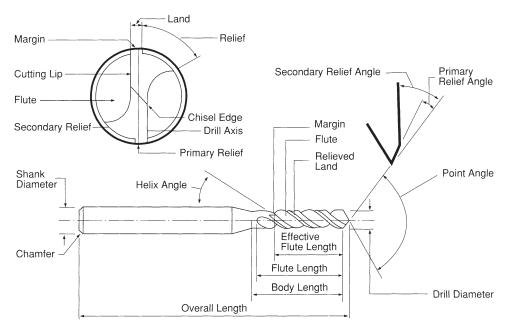

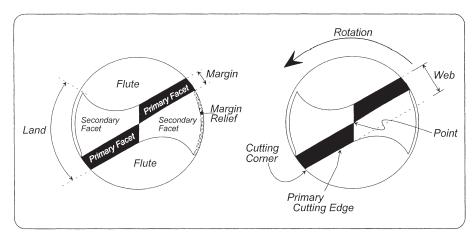

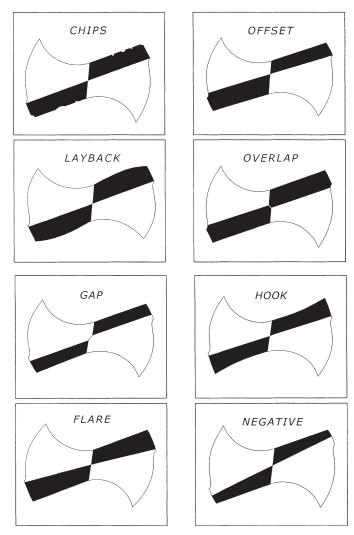

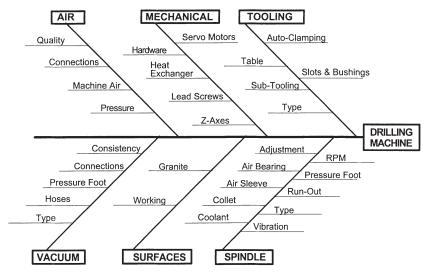

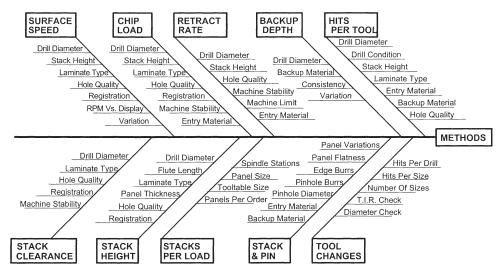

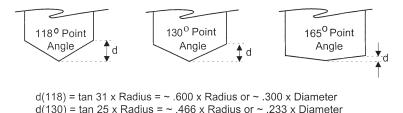

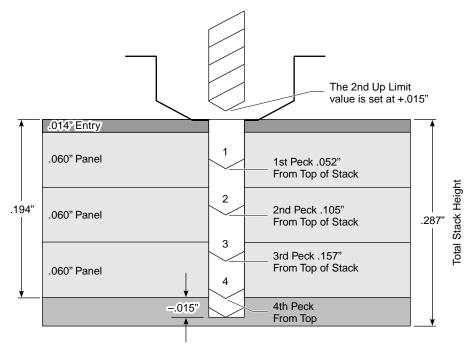

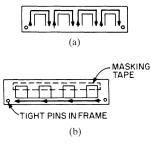

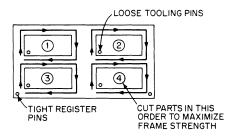

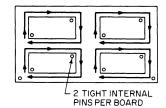

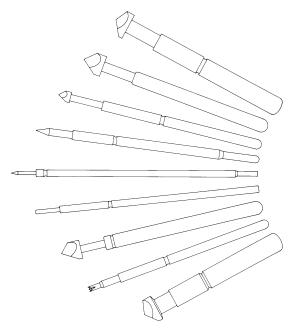

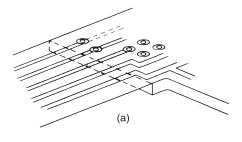

| 24.1 Introduction / 24.3 24.2 Materials / 24.4 24.2.1 Laminate Material / 24.4 24.2.2 Drill Bits / 24.5 24.2.3 Drill Bit Rings / 24.8 24.2.4 Entry Material / 24.9 24.2.5 Backup Material / 24.9 24.2.6 Tooling Pins / 24.10 24.3 Machines / 24.11 24.3.1 Air / 24.11 24.3.2 Vacuum / 24.12 24.3.3 Tooling / 24.12 24.3.4 Spindles / 24.12 24.3.5 Mechanical Factors / 24.14 24.3 Methods / 24.15 24.4.1 Surface Speed and Spindle Speed / 24.15 24.4.2 Chip Load and Infeed Rate / 24.16 24.4.3 Retract Rate / 24.16 24.4.4 Backup Penetration Depth / 24.16 24.4.5 Hits per Tool / 24.17                |      |

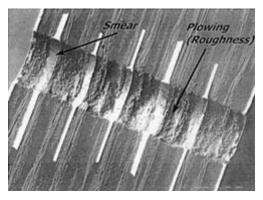

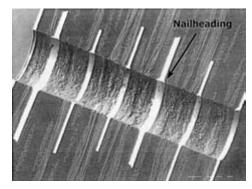

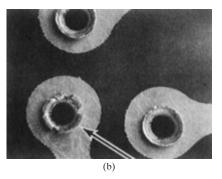

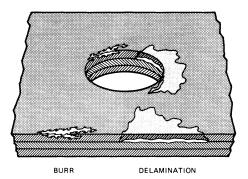

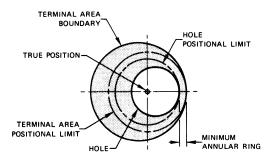

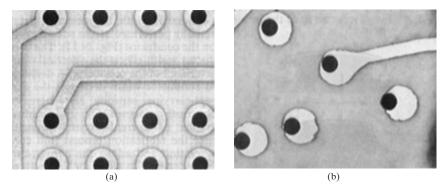

| 24.4.6 Stack Clearance Height / 24.17 24.4.7 Drilled Stack Height / 24.18 24.4.8 Stacking and Pinning / 24.18 24.5 Hole Quality / 24.18 24.5.1 Definition of Terms / 24.18 24.5.2 Examples of Drilled Hole Defects / 24.19 24.6 Postdrilling Inspection / 24.20 24.7 Drilling Cost per Hole / 24.20 24.7.1 Machine Time / 24.20 24.7.2 Drill Bits / 24.22 24.7.3 Entry and Backup Materials / 24.22 24.7.4 Burden and Labor / 24.22 24.7.5 Total Drilling Cost and Cost per Hole / 24.22                                                                                                                                                                                                                                                                                   |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

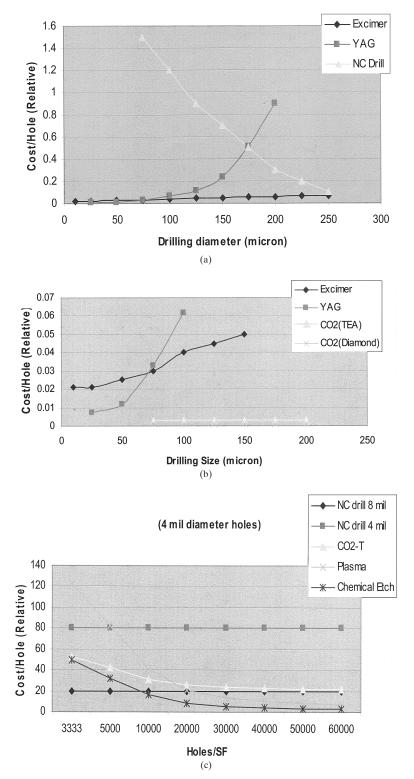

| Chapter 25. High-Density Interconnect Drilling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25.1 |

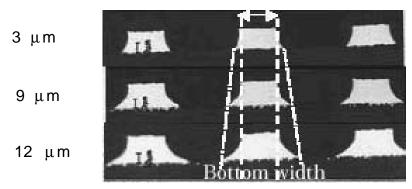

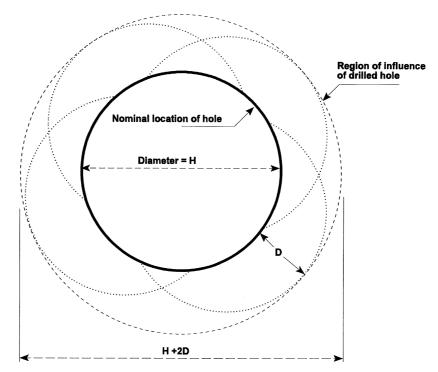

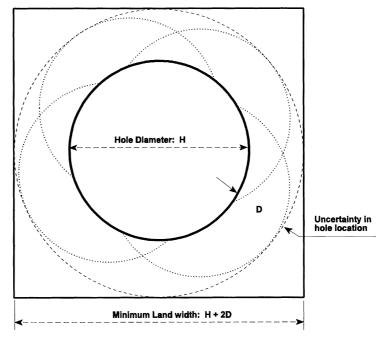

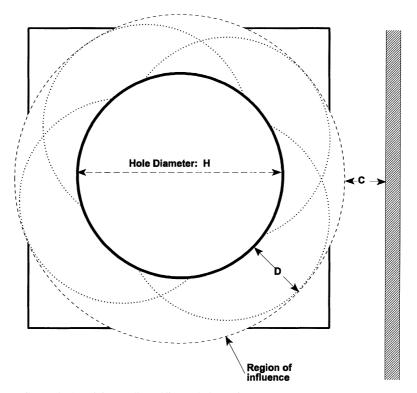

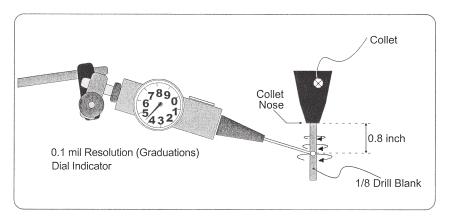

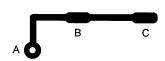

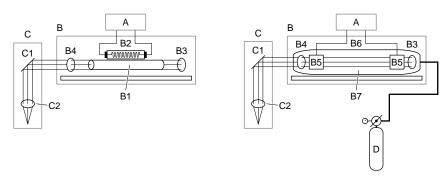

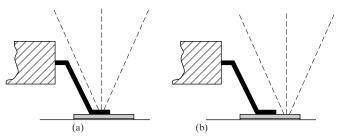

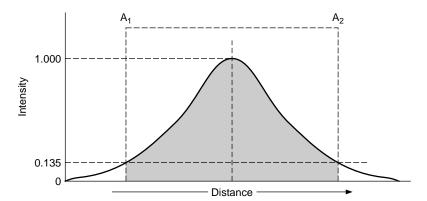

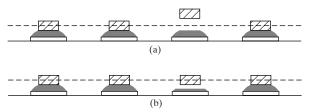

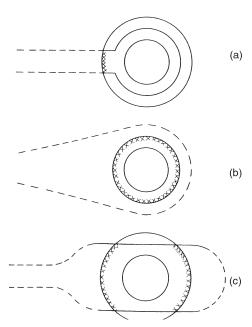

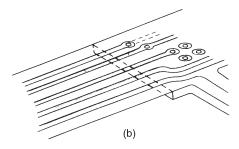

| <ul> <li>25.1 Introduction / 25.1</li> <li>25.2 Factors Affecting High-Density Drilling / 25.1</li> <li>25.2.1 Positioning/Hole Location / 25.2</li> <li>25.2.2 Predrilling Issues / 25.2</li> <li>25.2.3 Drill Room Temperature and Relative Humidity / 25.2</li> <li>25.2.4 Vacuum / 25.3</li> <li>25.2.5 Drill Bit Condition / 25.4</li> <li>25.2.6 Dynamic Spindle Run-out / 25.4</li> <li>25.2.7 Spindle Speed / 25.4</li> <li>25.2.8 Retraction Rate / 25.6</li> <li>25.3 Depth-Controlled Drilling Methods / 25.6</li> <li>25.3.1 Manual Through-Hole Drilling / 25.6</li> <li>25.3.2 Depth-Controlled Drilling / 25.6</li> <li>25.3.3 Controlled-Penetration Drilling / 25.7</li> <li>25.4.1 Peck Drilling / 25.7</li> <li>25.4.2 Pulse Drilling / 25.9</li> </ul> |      |

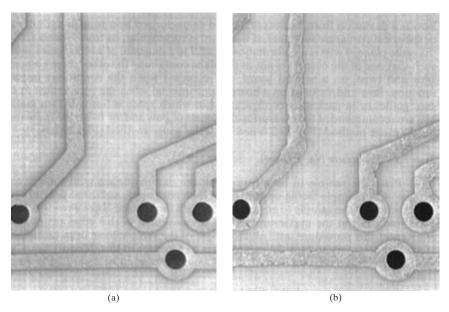

| Chapter 26. Imaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26.1 |

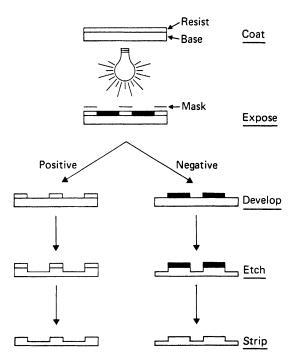

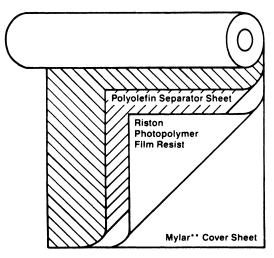

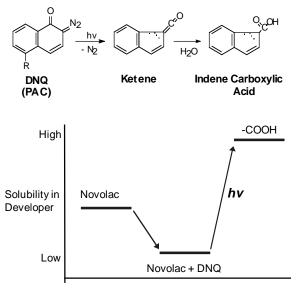

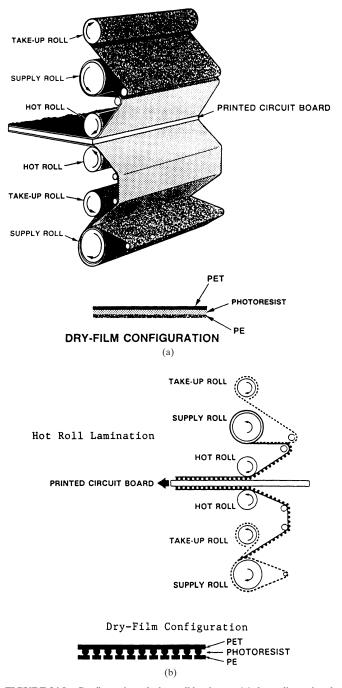

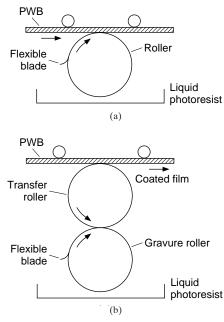

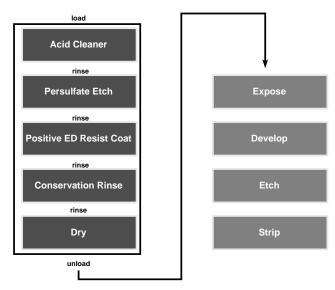

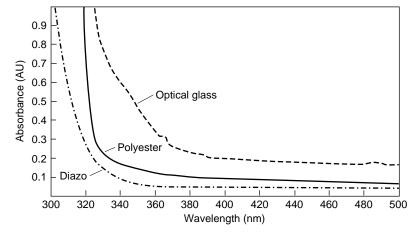

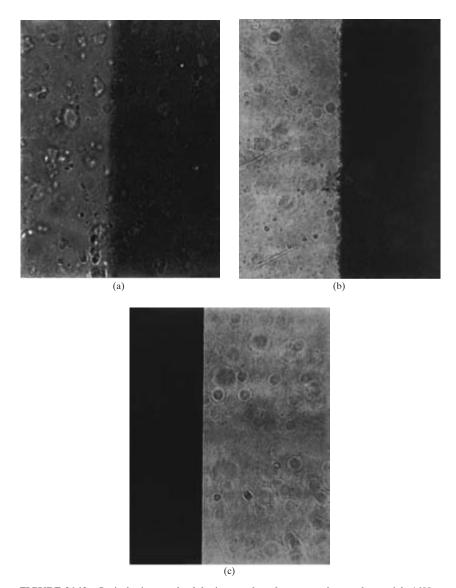

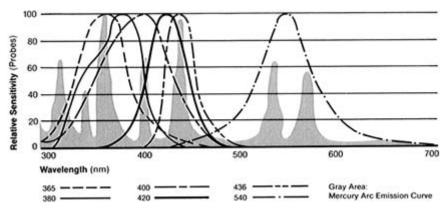

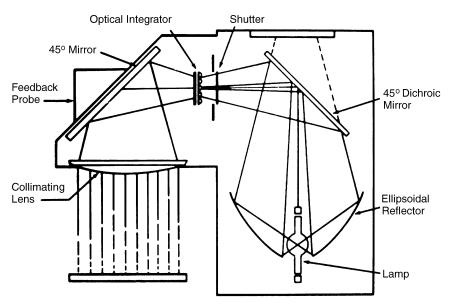

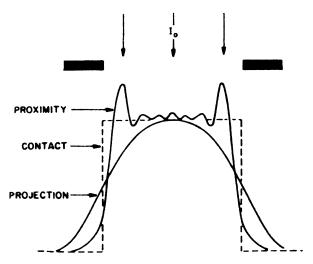

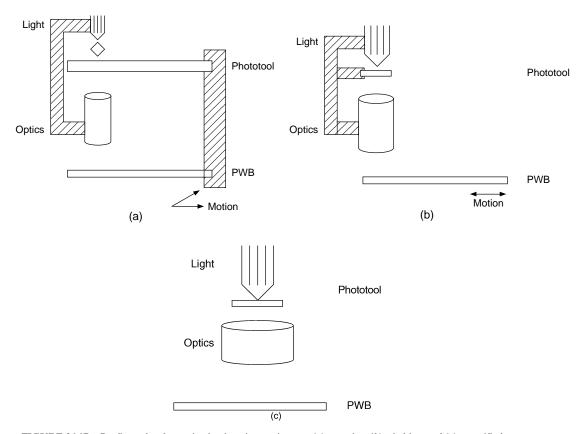

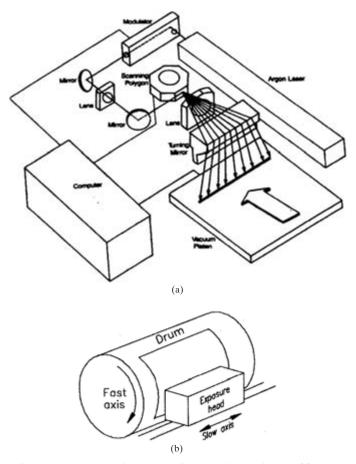

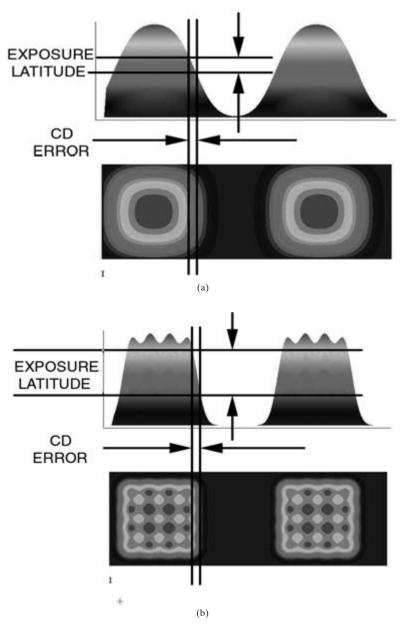

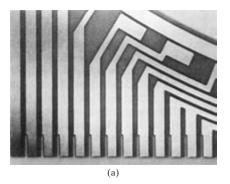

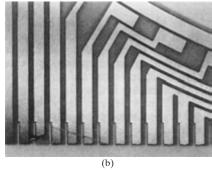

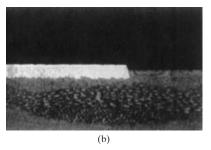

| 26.1 Introduction / 26.1 26.2 Photosensitive Materials / 26.2 26.2.1 Positive- and Negative-Acting Systems / 26.2 26.2.2 Decision Factors / 26.3 26.3 Dry-Film Resists / 26.4 26.3.1 Chemical Composition Overview / 26.5 26.3.2 Aqueous-Processable Dry Films / 26.5 26.3.3 Semiaqueous- and Solvent-Developable Dry Films / 26.6 26.4 Liquid Photoresists / 26.7 26.4.1 Negative-Acting Liquid Photoresists / 26.7 26.4.2 Positive-Acting Liquid Photoresists / 26.7 26.5 Electrophoretic Depositable Photoresists / 26.7 26.6 Resist Processing / 26.8 26.6.1 Cleanliness Considerations / 26.8 26.6.2 Surface Preparation / 26.9 26.6.3 Photoresist Application / 26.11 26.6.4 Expose / 26.16 26.6.5 Develop / 26.26 26.6.6 Strip / 26.27                              |      |

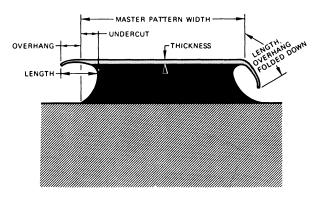

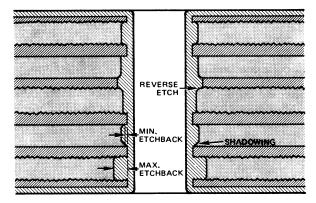

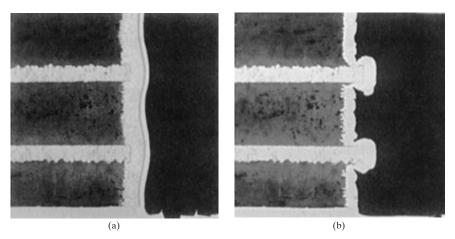

| 26.7 Design for Manufacturing / 26.27<br>26.7.1 Process Sequence: Etching vs. Plating Considerations / 26.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

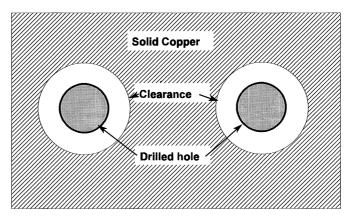

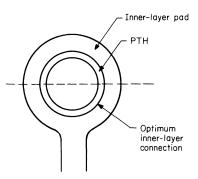

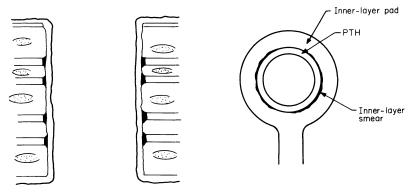

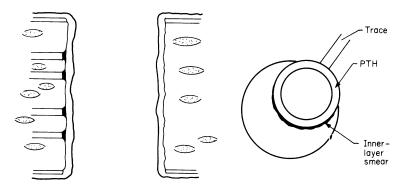

| 26.7.2 Line and Space Division for a Fixed Pitch / 26.28 26.7.3 PTH Capture Pad Size and Shape for Optimum Line Formation / 26.28 References / 26.29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |